国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)新原理コンピューティング研究センター 湯浅 新治 研究センター長、スピンデバイスチーム 薬師寺 啓 研究チーム長、デバイス技術研究部門【研究部門長 中野 隆志】 高木 秀樹 総括研究主幹らは、不揮発性メモリーMRAM用の単結晶記憶素子をシリコンLSIに集積化する製造プロセス技術を開発した。

不揮発性メモリーMRAMは、記憶素子である磁気トンネル接合(MTJ素子)からなる記録ビット、ビット選択に用いる半導体トランジスタ(CMOS)、それらを繋ぐ金属配線などで構成される。このメモリーは、酸化マグネシウム(MgO)トンネル障壁を用いた多結晶MTJ素子を多結晶の金属配線上に直接堆積することにより作製される。しかし、この従来からの技術では、多結晶MTJ素子の性能の不揃いや材料特性に起因して、MRAMの微細化が限界に達すると予想されるため、その解決策として新材料を用いた単結晶MTJ素子およびその集積化技術が注目されている。

今回、MgOに代わる新材料としてスピネル酸化物MgAl2O4を用いた単結晶MTJ薄膜を、直径300 mmのシリコンウエハー上に作製することに初めて成功した。また、ウエハー直接ボンディングを用いた3次元積層技術により、単結晶MTJ素子をMRAM用のシリコンLSIに集積化することにも初めて成功した。この技術は、現在主流の不揮発性メモリーSTT-MRAMの超微細化だけでなく、さらに省電力な電圧駆動MRAMや量子コンピューターの中核技術である超伝導量子ビットの高性能化などにも貢献する。なお、この技術の詳細は、2021年6月13~19日にオンライン開催される国際会議Symposia on VLSI Technology and Circuitsで発表される。

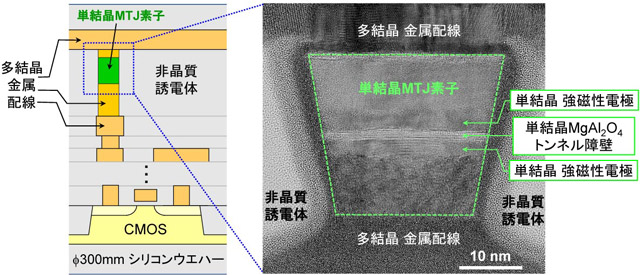

不揮発性メモリーSTT-MRAM(左)に集積化した単結晶MTJ素子の電子顕微鏡写真(右)

不揮発性メモリーMRAMは、読み書きが高速で書き換えの耐久性に優れるなどの特徴を持ち、情報処理の省電力化の観点から注目を集めている。現在のMRAM製品開発の主流は電流書き込み型MRAM(STT-MRAM)である。また、研究段階にある電圧書き込み型MRAM(電圧駆動MRAM)は、STT-MRAMよりも電力消費が少ないため、次世代の不揮発性メモリーとして期待されている。Society 5.0やポスト5G技術を実現するためには、5 nm技術世代以降に対応するMARMの微細化や高速メモリーSRAM並の省電力が鍵となる。現状では、MTJ素子の超微細化に伴う性能の不揃いの増大や性能不足などの問題のため、MRAM技術の改良だけでは微細化や省電力性の実現は困難である。

産総研は、大容量MRAMを実現するための中核技術として、2004年にMgOトンネル障壁を用いた高性能MTJ素子を発明し、STT-MRAM実現のためのブレークスルーとなった。これは、小さな単結晶基板上にエピタキシャル成長した単結晶素子であった(産総研プレス発表 2004年3月2日)。しかし、当時の技術では通常の製造プロセスによる単結晶MTJ素子の実用化は、多結晶の金属配線上にMTJ薄膜を形成するという制約のため不可能であった。そこで産総研はキヤノンアネルバ株式会社と共同で、多結晶MgOトンネル障壁とCoFeB合金電極を組み合わせた多結晶MTJ素子を開発し、その実用化を可能とした(産総研プレス発表 2004年9月7日)。その後、このCoFeB/MgO/CoFeB構造の多結晶MTJ素子の仕様が標準となり、現在までにSTT-MRAMやハードディスク磁気ヘッド、磁気センサーなどで広く利用されている。なお、多結晶MTJ素子では、MgOとCoFeBを他の材料に替えると性能が著しく劣化するため、新材料を用いることは困難である。

現状の多結晶MTJ素子の改良だけでは、MRAMの超微細化や次世代の電圧駆動MRAMの実現は困難である。具体的には、多結晶であるために必然的に生ずる性能の不揃いやMgOとCoFeBの材料特性に起因した性能限界などの問題が、微細化に伴って顕著になる。もし、単結晶MTJ素子を用いたMRAMの製造プロセスを実現できれば、原子レベルでの性能の均質性とMgOとCoFeBに替わる新材料の活用により、MTJ素子の性能向上が期待できる。

単結晶MTJ素子をMRAMに集積化するには、ウエハー直接ボンディングなどの3次元積層技術を活用する必要がある。3次元積層技術は半導体デバイス分野では実績があるが、MTJ素子では積層技術が確立されていなかった。MgOトンネル障壁の機械的な強度が弱いため、機械的ダメージが加わる3次元積層プロセスをMTJ素子に適用することは技術的に非常に難しい。これまで産総研では、多結晶MTJ薄膜を用いた3次元積層プロセスを開発してきた(産総研プレス発表 2017年5月16日)。今回、MTJ素子の3次元積層技術を量産に適した300 mmプロセスに用いて、新材料の単結晶MTJ素子をMRAMに集積化技術の開発に取り組んだ。

なお、本研究開発は、内閣府 革新的研究開発推進プログラム(ImPACT)「無充電で長期間使用できる究極のエコIT機器の実現(2014~2018年度)」、および経済産業省及び国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)が推進する「ポスト5G情報通信システム基盤強化研究開発事業」(JPNP20017)による支援を受けて行った。

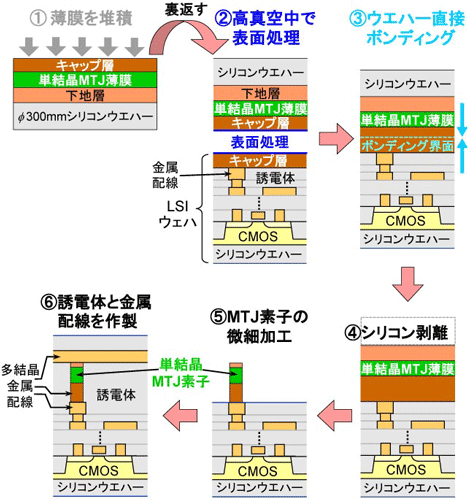

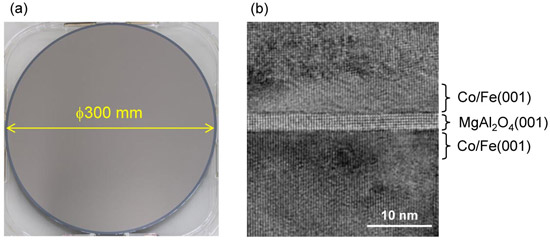

今回開発した3次元積層プロセス技術の概略を図1に示す。ステップ①で、直径300 mmの単結晶シリコンウエハー上に単結晶MTJ薄膜をエピタキシャル成長により堆積した(図2(a))。これまで単結晶MTJ薄膜は、小さな単結晶基板を用いた研究段階の技術であった。今回産総研では、この薄膜作製技術を発展させることにより、300 mmウエハー上に単結晶MTJ薄膜を作製することに初めて成功し、量産へのめどをつけた。また、新材料を比較的自由に用いることができるエピタキシャル成長の利点を活かして、MgOに代わり、より高品質なスピネル酸化物MgAl2O4を用いたトンネル障壁層を作製した。作製したMTJ薄膜の断面の電子顕微鏡写真を図2(b)に示す。作製した単結晶MTJ薄膜は、MgAl2O4トンネル障壁層とCo/Fe強磁性電極層の界面が原子レベルで平坦であり、結晶格子の欠陥がほとんど存在しない。これは、MgOに比べて格子整合性が良いMgAl2O4の特徴が活かされた結果であり、極めて高品質の単結晶MTJ薄膜が作製されている。

図1 単結晶MTJ素子の3次元積層プロセス

次にステップ②③のように、単結晶MTJ薄膜ウエハーと別途用意したMRAM用LSIウエハーの直接ボンディングを行った。ここで、産総研が独自に開発したタンタルキャップ層の表面平坦化技術を用いて原子レベルで平坦な薄膜表面を実現することにより、単結晶MTJ薄膜のウエハー直接ボンディングに初めて成功した。ステップ④のシリコン剥離プロセスでは、独自に調合したアルカリ溶液を用いたウェットエッチングにより、単結晶MTJ薄膜に損傷を与えずに裏面シリコンウエハーを除去することに成功した。

図2 (a)直径300 mmのシリコンウエハー上に作製した単結晶MTJ薄膜。

(b)単結晶MTJ薄膜の断面の透過電子顕微鏡写真

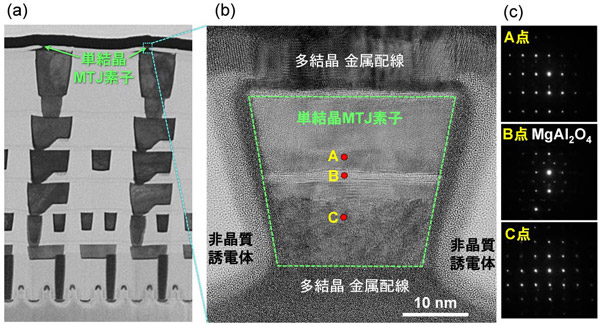

つづいてステップ⑤で、MTJ薄膜を微細加工して直径約25 nmの円柱状のMTJ素子を形成した。最後にステップ⑥で誘電体と上部の金属配線を作り込むことにより、ナノサイズの単結晶MTJ素子をSTT-MRAM用LSIに集積化することに初めて成功した。作製したLSIの断面の電子顕微鏡写真を図3(a)(b)に示す。ナノサイズの単結晶MTJ素子が、多結晶金属配線と非晶質誘電体の中に埋め込まれた構造が実現している。3次元積層プロセスを経た後もMTJ素子が単結晶を維持していることを確認するために、MgAl2O4トンネル障壁層とその上下の電極層のナノビーム電子線回折を観察した(図3(c))。図のように、格子状に配列した電子線回折スポットを観察しており、MTJ素子が結晶粒界が無い単結晶を維持していることを確認した。また、開発した単結晶MTJ素子の性能の不揃いが、従来型の多結晶MTJ素子に比べて小さいことも確認した。

図3 (a)LSI断面の電子顕微鏡写真。(b)MTJ素子周辺を拡大した電子顕微鏡写真。(c)ナノビーム電子線回折像

今後は、強磁性電極にも新材料を用いた単結晶MTJ素子を開発し、MRAMの超微細化や電圧駆動MRAMのための基盤技術として活用していく予定である。また、今回開発されたプロセス技術は、MTJ素子に限らず、他のトンネル接合素子にも広く応用できるものである。MTJ素子と並んで代表的なトンネル接合素子であるジョセフソン接合は、超伝導量子コンピューターの量子ビットを構成する要素技術として注目されている。現在、超伝導量子コンピューターを大規模化するための研究開発が世界規模で精力的に行われており、長いデコヒーレンス時間を持つ量子ビットの開発が重要課題の一つとなっている。現状、量子ビットのジョセフソン接合には非晶質のトンネル障壁と多結晶の超伝導電極が用いられている。今回開発したプロセス技術を応用して、ジョセフソン接合の単結晶化と新材料の導入を行い、長いデコヒーレンス時間を持つ量子ビットの開発を目指す予定である。