独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【研究部門長 金丸 正剛】フロンティアデバイスグループ 酒井 滋樹 研究グループ長らは、国立大学法人 東京大学(以下「東京大学」という)大学院 工学系研究科 竹内 健 准教授と共同で、強誘電体ゲート電界効果トランジスタ(FeFET)をメモリーセルとして用いるとNANDフラッシュメモリーの性能が著しく向上することを実証した。セルレベルで、従来型のNANDフラッシュメモリーのメモリーセルの書き換え回数が1万回、書き込み電圧が20Vなのに対して今回作製したメモリーセルの書き換え回数は1億回以上、書き込み電圧は6V以下である。従来のNANDフラッシュメモリーの微細化の限界は30nm程度といわれているが、今回作製したメモリーセルの技術を強誘電体NANDフラッシュメモリーに応用することにより、将来の20nm、10nm技術世代にも対応できるため、次世代高密度大容量不揮発メモリーとして期待される。

なお、この成果は、2008年5月18日 - 22日にフランスで開催の第23回不揮発性半導体メモリーワークショップ(23rd IEEE NVSMW / 3rd ICMTD‘08)で発表される。

|

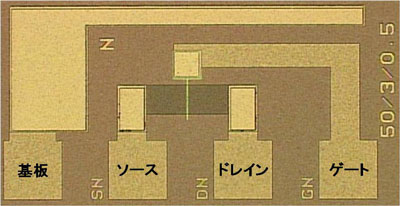

Fe-NANDフラッシュメモリーのためのFeFET光学顕微鏡写真

ゲート長3µm、ゲート幅50µm |

|

近年の携帯型情報機器の普及に伴い、より小型軽量で省電力な大容量データ記憶装置へのニーズが高まっている。大容量データ記憶装置として、モーターなどの機械部品を必要とするハードディスクドライブ(HDD)の代わりに、NANDフラッシュメモリーを用いたソリッドステートドライブ(SSD)が小型軽量で外的衝撃に強いことから注目されている。NANDフラッシュメモリーはHDDの磁気ディスクと比較して容量単価が高かったが、メモリー素子の集積度を上げて低価格化することで市場に急速に浸透してきた。

しかし、NANDフラッシュメモリーの書き換え回数は約1万回と決して多くなく、集積度を高めるために微細化を進めると、書き換え回数はさらに減少してデータの信頼性に不安が生じるといわれている。また、従来型のフラッシュメモリーのメモリーセルは、微細化を進めると隣接メモリーセルの浮遊ゲート間の容量結合ノイズ等の問題により30nm技術世代以降で微細化限界を迎えるといわれている。

FeFETをNANDフラッシュメモリーセルに用いた強誘電体NAND(Fe-NAND)フラッシュメモリーが実現すると、現在のNANDフラッシュメモリーと比べて書き換え可能回数の飛躍的に多いメモリーになるだけでなく、浮遊ゲートが存在しないために隣接メモリーセル間の容量結合ノイズが生じない等の理由により30nm技術世代以降の20nm、10nm技術世代の高密度大容量不揮発メモリーに適していると期待される。

産総研では、メモリーにもなるトランジスタとしてFeFETの研究を進めてきた。FeFETは1963年にその動作原理が提唱されて以来、データ保持時間の短さが問題となっていたが、産総研は2002年にPt/SrBi2Ta2O9/Hf-Al-O/Siというゲート構造を用いてデータ保持時間を長くすることに成功し、2004年に自己整合ゲート技術を用いてFeFETの微細化が可能であることを実証した(2002年10月、2004年12月プレス発表)。それ以降、FeFETを半導体集積回路へ実際に応用するための研究を続け、その一環として、東京大学 生産技術研究所の桜井貴康教授、東京大学 大規模集積システム設計教育研究センターの高宮真准教授にも一部協力を頂き、東京大学の竹内准教授とともにFeFETをNANDフラッシュメモリーへ適用することについて検討を重ねてきた。

なお、本研究は、独立行政法人新エネルギー・産業技術総合開発機構の「エネルギー使用合理化技術戦略的研究開発/エネルギー有効利用基盤技術先導研究開発/低消費電力プロセッサのための不揮発論理回路基盤技術の開発」の中で行われた。

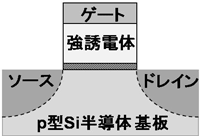

NANDフラッシュメモリーセルとして最適なしきい値をもつようにチャネル領域への不純物注入条件を調整したp型Si半導体基板上にパルスレーザー蒸着法によって高誘電体Hf-Al-O薄膜を約10nm、強誘電体SrBi2Ta2O9薄膜を約400nm製膜した後、金属Ptを約200nm製膜し、フォトリソグラフィー技術によりゲートおよびソース、ドレイン、基板の各電極を形成して金属-強誘電体-絶縁体-半導体(MFIS)ゲート積層構造をもつnチャネル型FeFETを作製した(図1)。

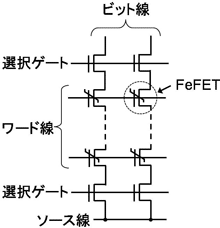

Fe-NANDフラッシュメモリーのアレイ構成を図2のように想定し、データ書き込み、一括消去、読み出し動作を行うことの出来る適切な電圧印加条件を詳細に検討した。FeFETにパルス幅の異なる書き込み・消去電圧を与えてからしきい値を測定したところ、10µs、6Vの高速・低電圧パルスによっても2つの記憶状態に相当するしきい値が十分に判別できた。また、メモリーセルにデータ書き込みやデータ読み出しを行う際に同時に隣接するメモリーセルに加わる電圧負荷条件(書き込みディスターブ、あるいは読み出しディスターブ)を、FeFETに加えてしきい値の変化を調べ、メモリーセルへの書き込みや読み出しによって、隣接するメモリーセルの記憶データが誤って書き換えられることのない電圧条件を得た。

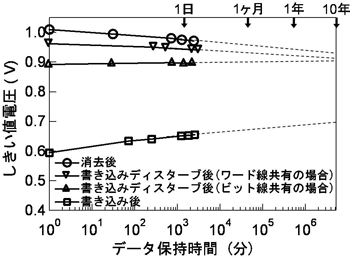

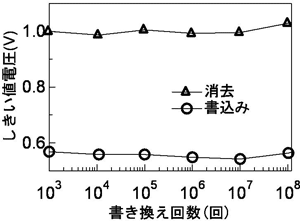

データ書き込み後、消去後、書き込みディスターブ後の各々のデータ保持特性(図3)から、このnチャネル型FeFETは外挿値で10年間のデータ保持が期待される。また、10µs、6Vの書き込み・消去電圧パルスを各々1億回まで印加してnチャネル型FeFETのしきい値の変化を調べたところ、1億回のパルス印加後でも大きなしきい値の変化は見られず(図4)1億回以上の書き換え耐性をもつことが示された。

以上のように、Fe-NANDフラッシュメモリーのメモリーセルとしてnチャネル型FeFETを作製し、書き換え回数1億回以上、書き込み電圧6V以下を実証した。このメモリーセルは、従来のフラッシュメモリーでは難しかった20nm、10nm技術世代の高密度大容量不揮発メモリーに適している。

|

図1 MFISゲート積層構造をもつnチャネル型

|

|

|

|

|

|

図2 Fe-NANDフラッシュメモリーのアレイ構成 |

|

|

|

|

図3 データ書き込み後、消去後、書き込みディスターブ後のデータ保持特性 |

|

図4 書き換え耐性 |

FeFETの微細化・集積化技術の開発を進めながら東京大学と共同でFe-NANDフラッシュメモリーアレイの回路設計と作製を行い、Fe-NANDフラッシュメモリーアレイの動作を実証する。