国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)デバイス技術研究部門【研究部門長 中野 隆志】 先端CMOS技術研究グループ 張 文馨 (Chang Wen Hsin) 研究員を代表とする日本チーム(産総研と東北大学)と国家実験研究院 台湾半導体研究中心(Taiwan Semiconductor Research Institute、以下「TSRI」という) の李 耀仁 (Lee Yao-Jen) リサーチフェローを代表とする台湾チーム(国立交通大学、国立成功大学、国立暨南国際大学、国立台湾大学、国立中山大学、逢甲大学、工業技術研究院、Hitachi High-Tech Taiwan Corporation)の日本-台湾国際共同研究グループは、2nm世代の電界効果トランジスタ(FET)とされるSi(シリコン)とGe(ゲルマニウム)の異種チャネル相補型電界効果トランジスタhCFET(heterogeneous Complementary-Field Effect Transistor)を開発した。

今回、SiとGeのチャネル薄膜を上下に積層させる技術を開発し、Si n型FETとGe p型FETを最短距離で連結するhCFET構造を実現した。集積回路の3次元的な構造縮小化により、大幅な集積化向上とさらなる高速化が期待できる。

なお、この技術の詳細は、2020年12月12~16日(12日発表)にオンラインで開催される2020 IEEE International Electron Devices Meeting (IEDM 2020) で発表される。

Si/Ge異種チャネル相補型電界効果トランジスタhCFET

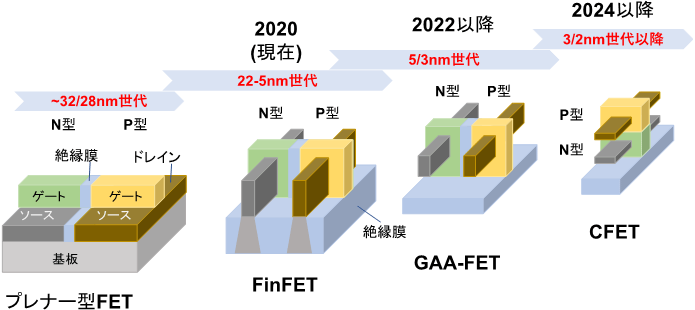

携帯情報端末やIT機器などの爆発的な普及により、電子情報機器の高性能化や消費電力の低減が求められている。図1に情報処理を担う電界効果トランジスタ(FET)構造のロードマップを示す。プレナーと呼ばれる平面型のCMOS構造はムーアの法則にそって、FETの微細化により高性能化と低消費電力化の両立が図られてきたが、2次元的微細化は物理的限界に達しており、22nm世代あたりから3次元的なFET構造に大きく変化した。FinFETは、ヒレ(Fin)状のゲート構造をもつFETで、現在実用化されている。その発展型が、ゲートがチャネルの上下、左右を完全に覆うようなGAA(Gate All Around)構造である。今後さらに進化したFET構造が、n型FETとp型FETを上下に積層したCFET構造と言われている。このような構造では、従来の単一FET 素子の寸法でCMOSを構成でき、大幅な面積縮小と高速化が図れる。一方、Si以外のチャネル材料の研究開発も進行している。Geは、Siに比べホール移動度が高く、低電圧動作が可能で、Siプロセスとの親和性が高いことから、n型FETは従来のSiで、p型FETはGeで作製できる異種チャネル集積プラットフォームがFETの高速化技術として期待されている。

図1 FET構造のロードマップ

産総研では、Si n型FETとGe p型FETを混載したCMOS技術の研究開発を、国立研究開発法人 新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト(2001~2010年度)」で開始し、独立行政法人 日本学術振興会 最先端研究開発支援プログラム(FIRST)(2009~2013年度)」で設置した連携研究体グリーン・ナノエレクトロニクスセンターを経て、現在はデバイス技術研究部門で行ってきた(2011年9月27日、2014年6月9日、2017年6月5日産総研プレス発表)。一方台湾のTSRIでは、2nm世代以降の3次元チャネル実現に向けた微細プロセス技術の開発を強力に推進している。2018年に、両者はそれぞれの強みを生かした国際共同研究プロジェクトを開始した。

なお、本研究開発は、科学技術振興機構(JST)国際科学技術協力基盤整備事業日本-台湾研究交流「AIシステム構成に資するナノエレクトロニクス技術」(研究主幹:金山 敏彦)の研究課題「AIチップ技術に向けた三次元異種機能集積hCFETs」(代表研究者:張 文馨、李 耀仁)の一環として行われた。

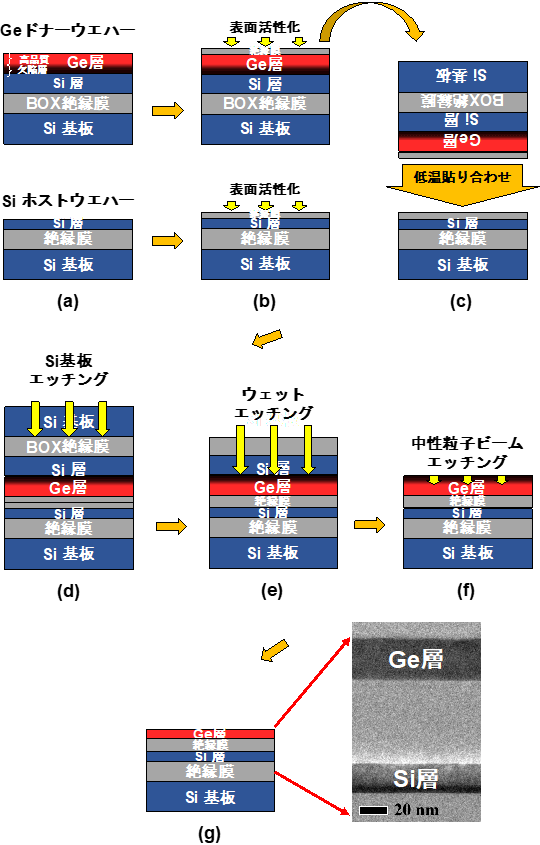

産総研とTSRIは日本-台湾国際連携を通じて、Si層とGe層が積層されたSi/Ge異種チャネル集積プラットフォームを構築した。SiやGeなどの熱膨張率の異なる材料の積層には、熱的ストレスの影響を避けるために、極力低温での積層プロセスが望まれる。われわれは、摂氏200度以下で高品質のSi層とGe層を積層する低温異種材料接合技術(Low Temperature Hetero-layer Bonding Technology, LT-HBT)を開発した(図2)。今回開発した技術では、まずSOIホストウエハーとその上にGeをエピタキシャル成長したドナーウエハー(a)を用意する。ここでGe層中には、Si層との界面に近いところに欠陥層が、表面側には高品質層が存在する。次にドナーウエハーとホストウエハーそれぞれにSiO2絶縁膜を堆積し、表面を活性化した後(b)、200度の低温で直接接合させる(c)。その後、ドナーウエハーのSi基板(d)、BOX絶縁膜、Si層を順次除去する(e)。最後に東北大で開発された低損傷で加工できる中性粒子ビームエッチング(Neutral Beam Etching, NBE)でGeを均一に薄膜化すると(f)、Si/Ge異種チャネル積層構造が得られる(g)。積層プロセスとエッチングプロセスをすべて低温で行うことで、Si層やGe層へのダメージが極めて少ない高品質のSi/Ge異種チャネル集積プラットフォームを実現した。また、この技術を用いると、hCFET作製プロセスの大幅な簡略化が図れるだけでなく、さらなる多層化構造にも対応できる。

図2 低温異種材料接合技術を使ったSi/Ge異種チャネル積層プロセス工程

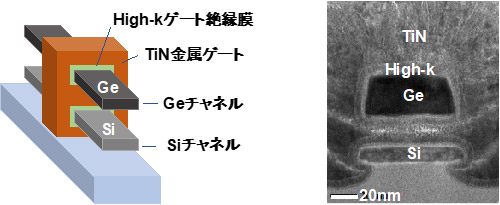

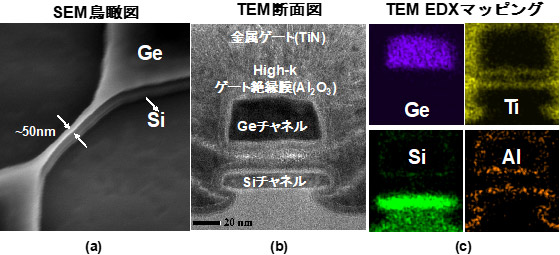

このSi/Ge異種チャネル積層プラットフォームから、hCFETを作製した(図3)。SiとGe層を同一のチャネルパターンで形成し、Si層とGe層の間の絶縁層をエッチングして、ナノシート状の積層型チャネル構造を得た。図3(a)のSEM鳥瞰図から、GeとSiチャネルが露出しているのがわかる。この構造に、high-kゲート絶縁膜/金属ゲートをチャネル全体を覆うように堆積させると、GAA構造のSi n型FETとGe p型FETが上下に積層されたhCFETが実現した(図3(b))。上部にGe層、下部にSi層がチャネル幅50nm程度のナノシート状で積層した構造が見て取れる。TEM EDX分析からは、Si/Ge異種材料チャネルがhigh-kゲート絶縁膜(Al2O3)と金属ゲート(TiN)に覆われていることがわかる(図3(c))。さらに、単一のゲートでこれらのn型FETとp型FETを同時にトランジスタ動作させることに成功し、LT-HBTによる異種チャネル積層化が2nm世代のトランジスタ技術として極めて有効であることが示された。

今回、日本-台湾の強固な国際連携により、2nm世代の3次元異種チャネル相補型電界効果トランジスタhCFETが初めて開発された。高速情報処理を低消費電力で行える大規模集積回路実現へ新たな一歩といえる。

図3 Si n型FET/Ge p型FETを上下積層した3次元異種チャネル相補型電界効果トランジスタ(hCFET)

今後、日本-台湾国際共同研究グループは、精度の高い異種チャネル集積プラットフォームを確立し、量産化への指針を示すことで、3年程度をめどに海外を含む民間企業への技術移転を目指す。