独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】新材料・機能インテグレーショングループ 森 貴洋 研究員らは、大規模集積回路(LSI)の3次元(3D)積層技術の実現に向けて、新たな多結晶膜形成技術を開発し、N型多結晶ゲルマニウム(Ge)トランジスタの性能を大幅に改善した。

多結晶Geは、広く用いられている多結晶シリコン(Si)に比べ、より低温(500 ℃以下)で形成できる。そのため、熱的ダメージを与えずに集積回路上にCMOS回路を直接積層でき、3D-LSIの要素技術として有望である。さらに、Ge中の電子や正孔の移動度はSiよりも高いために、高速動作や低電圧動作が期待される。集積回路動作にはN型とP型のトランジスタが必要である。多結晶GeのP型トランジスタでは既に通常の単結晶Siトランジスタに迫る十分な性能が得られているが、N型トランジスタの電流駆動力は通常のSiトランジスタよりも一桁以上低いという問題があった。今回開発した技術により、電流駆動力を従来の約10倍に増大できたため、多結晶Ge集積回路の動作速度が実用レベルになると期待され、3D-LSIの実現に貢献すると考えられる。

なお、この技術の詳細は、2014 年12 月15~17 日(米国太平洋時間)に米国・サンフランシスコで開催される「2014 International Electron Device Meeting」で発表される。

|

|

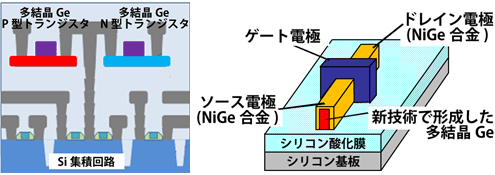

多結晶Geトランジスタを用いた3D-LSIのコンセプト図(左)と今回開発した多結晶Geトランジスタの構造模式図(右) |

多くの人がスマートフォンやタブレットなどのIT 機器を持つ時代となり、情報処理量は爆発的に増加している。IT機器の情報処理能力のさらなる向上が望まれる一方で、IT 機器による消費電力が増え続けており、低エネルギー消費社会の実現のためにはIT 機器の超低消費電力化も重要である。これまで、LSIの高性能化・低消費電力化はトランジスタの微細化によって実現されてきたが、技術的・経済的に一層の微細化が困難となってきている。一方、複数のLSIを積層した3Dの集積回路は、微細化技術によらずに、高集積化や高機能化を実現するとともに、配線遅延の低減による省電力化も実現できる。別々に作成したLSIを薄膜化して積層する手法が開発されているが、コストが高く、配線の密度が十分に高められないといった問題がある。そこで、新たな3D積層技術として、CMOS集積回路の配線層中にCMOS回路を連続的に積層し、上下の配線で接続して形成する3D-LSI技術が有望と考えられている。

産総研ナノエレクトロニクス研究部門に2014 年3 月末まで置かれていた連携研究体グリーン・ナノエレクトロニクスセンター(以下「GNC」という)では、新材料・新構造CMOS開発グループの手塚 勉 研究分担者、臼田 宏治 特定集中研究専門員(ともに現在は株式会社東芝)らと共同でLSIの低消費電力化と高性能化の両立を目指し、多結晶Geを用いたP型およびN型MOSFETに関する研究開発を行ってきた(2013 年12 月12 日 産総研プレス発表)。今回、新規な製造工程の導入により、N型多結晶Geトランジスタのさらなる性能向上を実現した。

なお本研究開発は、総合科学技術会議により制度設計された、独立行政法人 日本学術振興会の最先端研究開発支援プログラム(FIRST)の助成を受けて、GNC において実施した(2010 年度から2013 年度)。

トランジスタを形成する多結晶Ge膜は、Si基板上に熱酸化膜(SiO2)を形成し、その上に、スパッタリング法によって非晶質のGe膜を堆積し、フラッシュランプ・アニール(FLA)法による熱処理によって結晶化させて形成している。この多結晶Ge膜を用いてトランジスタを形成した場合、熱処理以降のプロセス温度は最高350 ℃であり、下地に銅配線を含む集積回路があっても、ダメージを与えずにすむ。試作したトランジスタは、概要に示した図(コンセプト図と構造模式図)に示すようなフィン形状をもつ無接合型トランジスタ構造である。無接合型のN型トランジスタは、チャネルとソース・ドレイン部をすべてN型とする必要がある。ところが、多結晶Geは通常はP型であるので、今回、多結晶Ge層を、品質を保ちながらN型化するために、結晶化のための第一のFLA法による熱処理後に、N型不純物(リン)を注入し、この不純物を活性化するため再度FLA法による熱処理を行った(図1)。この2段階FLA法によって高品質なN型多結晶Ge膜が作製できた。

|

|

図1 2段階FLA法を用いたN型トランジスタ作成プロセス |

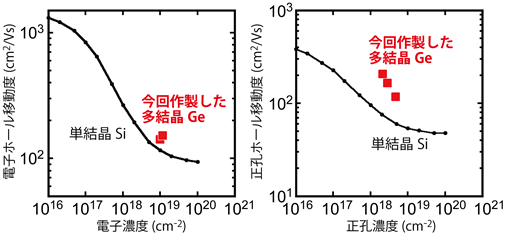

まず、この方法で作製した多結晶Ge膜の品質を表すホール効果移動度を図2に示す。N型(電子)とP型(正孔)のどちらの多結晶Ge膜も、単結晶Siを上回る移動度であった。これは、今回開発した方法による多結晶Ge膜を用いて単結晶Siを超える性能を持つトランジスタを実現できることを示している。

|

|

図2 今回開発した方法で作製した多結晶Geのホール効果移動度 |

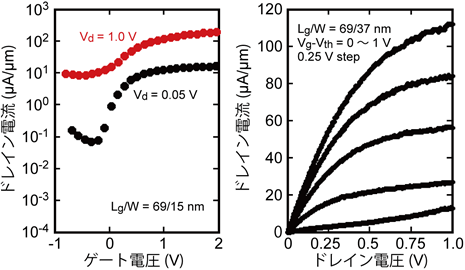

このように作製したN型多結晶Ge膜をフィン形状に加工し、さらにソースとドレインとの接合領域にニッケルとゲルマニウムの合金(NiGe合金)を形成することで無接合型のN型多結晶Geトランジスタ(ゲート長70 nm)を作製した。図3に、伝達特性と入出力特性を示す。1 Vの動作電圧でのドレイン電流値は約120 µA/µmに迫り、従来の約10倍もの値が得られた。これは、ほぼ同サイズの多結晶SiのN型MOSFETと同等である。2段階FLA法により不純物の活性化率が従来よりも向上し、寄生抵抗が低減したことが要因と考えられる。今回開発した技術により、これまで多結晶Geトランジスタにおいて集積回路動作のボトルネックと考えられていたN型トランジスタの動作速度が、著しく改善された。多結晶Geトランジスタと比較される多結晶Siトランジスタは、一般に単結晶Siトランジスタに比べて性能が劣る。すでに、P型の多結晶Geトランジスタの性能は多結晶Siトランジスタの性能を超えて単結晶Siトランジスタの性能に匹敵しているので、多結晶Geによる高性能CMOS集積回路の実現に大きく前進したといえる。

|

|

図3 今回作製したN型多結晶Geトランジスタの伝達特性(左)と入出力特性(右) |

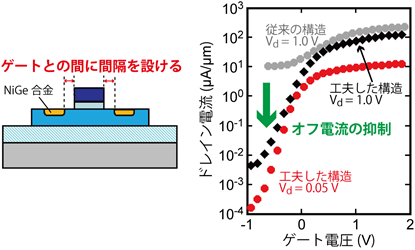

図3の伝達特性ではオフ電流が大きく、1 V印加時のオンオフ比は10程度にとどまっている点が問題であった。そこで、オフ電流低減のため、NiGe電極とゲートとの間に間隔を設けた構造を導入したところ、オフ電流が約1000分の1に低減した(図4)。オン電流は若干減少するが、NiGe電極とゲートとの間隔を最適化することで高いオン電流と低いオフ電流の両立が期待できる。

|

|

図4 工夫したデバイス構造の模式図(左)とその伝達特性(右) |

今後は、多結晶GeのP型トランジスタとN型トランジスタを組み合わせた集積回路を絶縁膜上に形成し、回路動作の実証を目指す。そして、多結晶Geを積層した3D-LSIの実現による、LSIの大幅な小型化と高機能化、低消費電力化を目指す。