国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)エレクトロニクス・製造領域【領域長 金丸 正剛】(以下「エレ製造領域」という)は、令和元年9月1日に「産総研・東大 AIチップデザインオープンイノベーションラボラトリ」(AIST-UTokyo AI chip Design open innovation Laboratory;AIDL)を国立大学法人 東京大学【総長 五神 真】(以下「東大」という)大規模集積システム設計教育研究センター【センター長 藤田 昌宏】(以下「VDEC」という)と共同で設立しました。産総研のオープンイノベーションラボラトリ(OIL)は、産総研の第4期中長期計画(平成27年度~令和元年度)で掲げている「橋渡し」を推進していくための新たな研究組織の形態で、AIDLがその第八号となります。東大としては、平成28年6月1日に東大柏キャンパス内に設置されたOPERANDO-OILに続き第二号となります。

実空間からのビッグデータを高効率に処理するためには、エッジ側でAI処理を行うことができるエッジコンピューティングが重要となります。エッジ側では、AI処理を行うデジタル回路はもちろんのこと、データ取得や通信のためのセンサーやアナログ回路を併せて搭載する必要がありますが、限られた電力やスペースの中でデータ取得(センシング)、通信(アナログ)、データ処理(デジタル)のシステム全体を最適化するためには、デジタル・アナログ・センサー(Digital Analog Sensor: DAS)統合設計技術が必要不可欠となります。

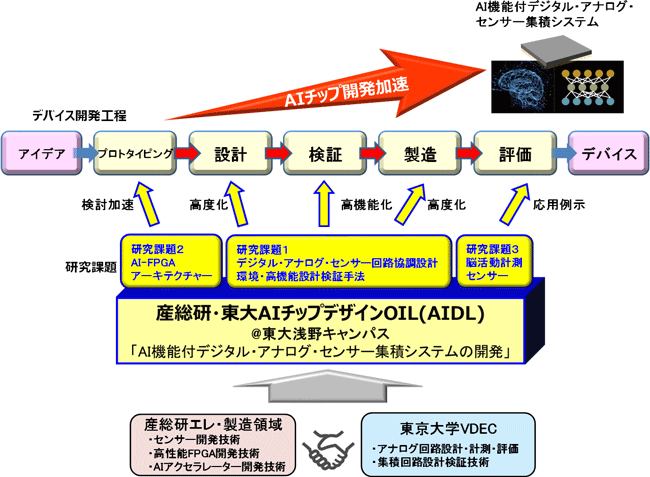

東大VDECでは、半導体集積回路設計について世界をリードする革新的な研究が行われています。また、デジタル回路のみならず、アナログ回路やMEMS回路の開発ならびに計測、検証、評価に関しても十分な実績を有しています。一方、産総研エレ製造領域では、センサーおよびAIチップ開発においてさまざまな成果を上げており、また、実際に脳活動計測用センサーや独自FPGAをはじめとする集積回路開発まで行っています。

そこで、産総研と東大は新たな産総研の拠点(AIDL)を東大浅野キャンパス内に設置し、東大の集積回路設計・評価・計測技術と産総研のシステム応用技術を合わせ、エッジ側で高効率なデータ取得と処理を可能とするAI機能付DAS集積システムの設計・検証・評価・計測といった開発環境を構築し、システム開発を推進します。さらに、構築した集積回路開発環境や、開発したシステムを産業界に橋渡しを行い、わが国のAIチップの開発の加速を目指します。

|

|

産総研・東大 AIチップデザインオープンイノベーションラボラトリ |

研究課題1:DAS集積システムの設計・検証・評価手法の研究

エッジコンピューティングでは、AI処理を行うデジタル回路、データ取得や通信のためのセンサーやアナログ回路を搭載するシステムが必要不可欠です。本研究では、AI機能付デジタル・アナログ・センサー(DAS)集積システムを実現するためのアナログ・デジタル要素技術やシステムアーキテクチャー、設計検証手法の研究を行います。

研究課題2:AI機能を回路に実装するための基盤研究

AI技術が日常生活にさらに深く浸透していくためには、ハードウエアとソフトウエアの両軸からのアプローチが必要不可欠です。本研究では、AI処理に適したFPGAアーキテクチャーの探索、ならびにAI処理に特化したFPGA開発アセットの構築、およびAIアクセラレーターを用いた医療用、工業用などの画像解析応用技術の開拓などのAI実装技術の研究開発を行います。

研究課題3:脳活動計測用のAI機能付きDAS集積システムの開発

ヒトの身体機能、認知機能などを補助する一手法として、電気・光・磁気などによる脳活動計測を行うことや刺激を与えることは有効なアプローチであることが知られています。本研究テーマにおいては、これらの計測・刺激を行うためのデバイスとして、センサー・アナログ・デジタルLSIおよび信号処理に関する基盤技術の創出と、これらを活用した脳活動計測応用(ブレインマシンインターフェース:BMIなど)に向けたシステム開発を行います。