- スパッタリング法で、原子レベルで制御されたSb2Te3層状物質を形成

- MoS2との異種層状物質界面(ファンデルワールス界面)形成で低コンタクト抵抗を実現

- 耐熱性があり量産も見込め、次世代CMOSデバイスの実現に貢献

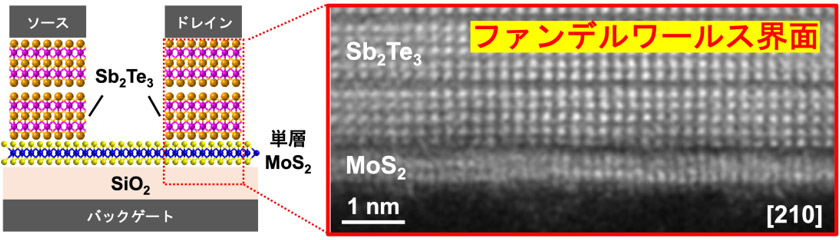

低コンタクト抵抗を有するMoS2トランジスタ

(左)トランジスタの模式図、(右)Sb2Te3/MoS2界面を拡大したTEM画像

※原論文「Sb2Te3/MoS2 van der Waals Junctions with High Thermal Stability and Low Contact Resistance」の図を引用・改変したものを使用しています。

クリエイティブ・コモンズ・ライセンス(表示4.0国際)

国立研究開発法人 産業技術総合研究所(以下「産総研」という)デバイス技術研究部門 張 文馨(Chang Wen Hsin) 主任研究員、畑山 祥吾 産総研特別研究員、齊藤 雄太 研究グループ付、岡田 直也 主任研究員、入沢 寿史 研究グループ付らは、東京都立大学 宮田 耕充 准教授と共同で三テルル化二アンチモン(Sb2Te3)/二硫化モリブデン(MoS2)のファンデルワールス界面の作製に成功し、n型MoS2トランジスタ性能向上に大きく貢献する接触界面抵抗の低減(低コンタクト抵抗)技術を開発しました。

MoS2は、2次元結晶構造を有する遷移金属ダイカルコゲナイド(TMDC)と呼ばれる材料であり、次世代トランジスタのチャネル用半導体材料として非常に注目されています。しかしながら、一般的な金属電極とMoS2接触面の高いコンタクト抵抗がトランジスタ高性能化の妨げとなっていました。今回、MoS2上に層状物質Sb2Te3を成膜することで、トランジスタのコンタクト抵抗を大幅に低減することに成功しました。また、Sb2Te3の高い熱安定性により、作製したMoS2トランジスタは半導体製造工程に対して十分な耐熱性を示すことが期待できます。今回開発した技術は、MoS2トランジスタにおけるコンタクト抵抗の課題を根本的に解決できる可能性を秘めており、次世代ロジック半導体として期待される2次元材料トランジスタの高性能化に大きく貢献します。

なお、本研究の詳細は、2023年2月10日(中央ヨーロッパ時間)にエレクトロニクスに関連した材料を取り扱う国際学術誌「Advanced Electronic Materials」に掲載されます。

先端CMOS製造技術において、電力効率や性能、面積、コスト「PPAC(Power efficiency, Performance, Area, Cost)」を改善し続けていくためには、単に大きさを小さくするだけではなく、新しい材料やデバイス構造を導入する必要があります。この技術的取り組みのなか、現行のシリコン(Si)においてはナノシート構造が提案され、2 nm世代の技術として期待が持たれています。さらにその先のBeyond 2 nm技術についても、経済産業省の半導体・デジタル産業戦略検討会議において、開発の強化が言及されています。Beyond 2 nm技術の一つとして、適度なバンドギャップを保ちつつ、化学的に安定な層状構造を有し、原子層厚においてSiよりも優れた半導体特性を示す2次元TMDC材料のトランジスタへの導入が期待されています。しかしながら、2次元材料トランジスタの実用化を実現するためには技術的に克服すべき課題が多く残されており、世界中の研究機関・企業で研究が盛んに行われてきました。

TMDCは1 nm以下の原子層領域においても高い導電性が維持できるという観点から、次世代トランジスタのチャネル材料として大きく注目されています。産総研では、国立研究開発法人科学技術振興機構 戦略的創造研究推進事業チーム型研究 (CREST) 「原子層ヘテロ構造デバイスの実証と3次元集積LSIのための原子層成膜プロセスの開発(2017~2021年度): 都立大との共同実施」プロジェクトにて高性能TMDCトランジスタの研究を実施してきました。従来のTMDCトランジスタ開発では、主にタングステン(W)、チタン(Ti)、クロム(Cr)、ニッケル(Ni)、パラジウム(Pd)、金(Au)などの金属電極が用いられてきました。しかしながら、これらの金属電極とTMDCとの界面は高いコンタクト抵抗を示すために、TMDCトランジスタの駆動電流が抑制され、デバイス性能が向上しないことが知られていました。これは、金属電極/TMDC接合界面でフェルミ準位のピンニング現象(FLP)が起こり、界面の電位障壁を低減することが困難であるためです。最近、半導体メーカーや研究機関を中心に、FLPを解消するようなTMDCのコンタクト形成技術についての開発が進められています。TSMCやIntelより、ビスマス(Bi)やアンチモン(Sb)といった半金属をコンタクト材料として用いることで、コンタクト抵抗が大幅に低減することが報告されています。しかし、Biは融点が低く(約270 ℃)、熱的安定性が低いことから、400 ℃以上の耐熱性が要求される半導体製造工程への適用は困難と考えられています。そのため、次世代トランジスタの高性能化に向けて、耐熱性が高くかつTMDCとのコンタクト抵抗を低減するような電極材料の開発が求められています。

なお、本研究開発は、JST CREST、JST FORESTプロジェクトおよびJSPS科研費による支援を受けています。

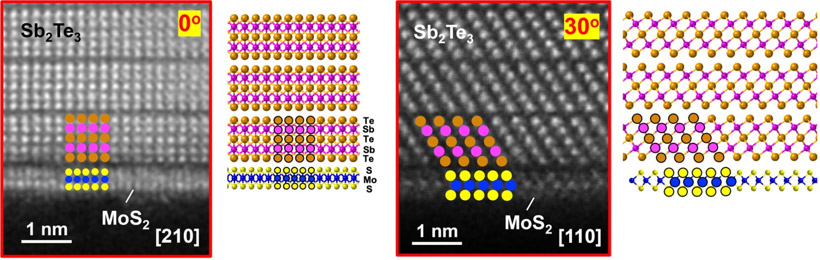

本研究では、代表的なTMDCの一つであるMoS2を用いたトランジスタを作製し、そのコンタクト材料としてSb2Te3に着目しました。Sb2Te3は、多数の原子が層状になっており、層同士はファンデルワールス力という弱い結合で結びついています。また、Sb2Te3は、BiやSbのように半金属に似た特性(狭バンドギャップ:0.2–0.3 eV)を示します。さらに、Sb2Te3の融点(約620 ℃)はBi等に比べて高いことが知られています。これらの特徴は、Sb2Te3が同じく層状物質であるMoS2との間にファンデルワールス界面を形成し、FLPを抑制する可能性があることを示唆するものです。このため、Sb2Te3を利用することで、高い耐熱性を維持したまま低コンタクト抵抗を実現できると考えました。産総研のグループは、これまでのSb2Te3の長い研究で、基板や下地材料表面に平行に層状物質を形成するノウハウを蓄積してきました。そこで、今回、量産化に適したスパッタリング法を駆使して単層MoS2上にSb2Te3を成膜し、Sb2Te3/MoS2の接触界面にファンデルワールス界面が形成されることを透過電子顕微鏡(TEM)によって確認しました。図1にSb2Te3/MoS2積層膜構造のTEM断面写真図および対応する原子配列を示します。Sb2Te3およびMoS2は両方とも良好な結晶性を持つ層状構造になっていることがわかりました。Sb2Te3/MoS2のTEM写真は、二つの材料の原子配列が一致していることを示しており、これらの積層膜がファンデルワールス界面を有することを確認しました。

図1 Sb2Te3/MoS2界面の断面電子顕微鏡(TEM)写真および対応する原子配列

※原論文「Sb2Te3/MoS2 van der Waals Junctions with High Thermal Stability and Low Contact Resistance」 の図を引用・改変したものを使用しています。

クリエイティブ・コモンズ・ライセンス(表示4.0国際)

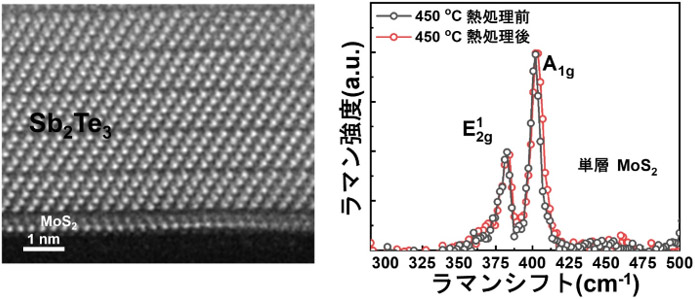

一般的に、集積回路の配線工程では400 ℃以上の耐熱性が実用化の重要な要件となります。そこで、Sb2Te3/MoS2積層膜構造の耐熱性を調べました。熱処理前後に、MoS2単層構造を維持していることを、ラマン分光法を用いた分析により確認しました。また、断面TEM写真(図2)より、Sb2Te3/MoS2積層膜構造は450 ℃の熱処理を経ても良好な結晶性とファンデルワールス界面を維持していることを明らかにしました。

図2 450 ℃熱処理後Sb2Te3/MoS2断面の電子顕微鏡写真およびラマンスペクトル

※原論文「Sb2Te3/MoS2 van der Waals Junctions with High Thermal Stability and Low Contact Resistance」 の図を引用・改変したものを使用しています。

クリエイティブ・コモンズ・ライセンス(表示4.0国際)

Sb2Te3/MoS2ファンデルワールス界面形成がトランジスタ特性にどのような影響を与えるかを調べました。図3にMoS2トランジスタの電流電圧特性の比較を示します。n型トランジスタ動作を示しつつ、Sbや、Ni、Wをコンタクト材料として使用した場合と比べて、Sb2Te3電極を有するトランジスタの駆動電流は4〜30倍にも向上することがわかりました。このような大幅な駆動電流の増大はコンタクト抵抗の低減が主要因であると考え、実際にMoS2トランジスタのコンタクト抵抗を求めた結果を図4に示します。Sb2Te3電極を有するトランジスタのコンタクト抵抗値は、Sb電極を使用した場合のそれと比べて1桁程度低く、また、これまでの世界最小の報告であるBi電極を使用した場合のコンタクト抵抗値とも遜色のない値であることがわかりました。SbやBi電極は半導体製造の後工程の高温に耐えないため、半導体デバイスへの使用には適しません。Sb2Te3電極は400 ℃以上の耐熱性を示しつつ、Bi電極に匹敵する低いコンタクト抵抗値を実現しており、これを両立したという報告は世界でも本研究が初となります。

以上のように、Sb2Te3/MoS2界面において低コンタクト抵抗と半導体製造工程に必要な耐熱性が両立できる技術を開発しました。この技術は、Beyond 2 nm世代のロジック半導体の実現に寄与するものとなります。

今後は、n型とp型のTMDCトランジスタを直列につないだCMOSを作製することを目指します。そのためにも、n型MoS2トランジスタだけでなく、p型TMDCトランジスタにおける低コンタクト抵抗技術の開発が求められます。今回開発したSb2Te3コンタクト技術は、n型MoS2に対して最適な特性を示しましたが、p型TMDCには別のコンタクト材料が必要となります。既存のSiの性能をはるかに超えた次世代ロジック半導体の実現に向けて、低コンタクト抵抗を有するTMDCによるCMOSの開発を加速していく計画です。

掲載誌:Advanced Electronic Materials

論文タイトル:Sb2Te3/MoS2 van der Waals Junctions with High Thermal Stability and Low Contact Resistance

著者:Wen Hsin Chang*, Shogo Hatayama, Yuta Saito*, Naoya Okada, Takahiko Endo, Yasumitsu Miyata, and Toshifumi Irisawa*

DOI:10.1002/aelm.202201091