NEDOは「AIチップ開発加速のためのイノベーション推進事業」に取り組んでおり、産業技術総合研究所、東京大学と共同で、ネットワークの末端などに使われるエッジ向けAIチップの設計を容易にするために、東京大学浅野キャンパス(東京都文京区)内に整備を進めている「AIチップ設計拠点」で、AIチップに使用されるAIアクセラレータ開発のための評価プラットフォームの構築を進めています。このたび、本評価プラットフォームの実証チップである「AI-One」において、仕様が異なる6種類のAIアクセラレータを同一チップに搭載し、その試作チップを評価した結果、設計通りの周波数での動作を確認しました。

AIチップを開発する中小・ベンチャー企業などは本評価プラットフォームを使うことにより、各企業が設計したAIアクセラレータ搭載のAIチップを擬似的に作成できるため、短期間(従来比45%以下)に低コストで設計と評価が可能になります。

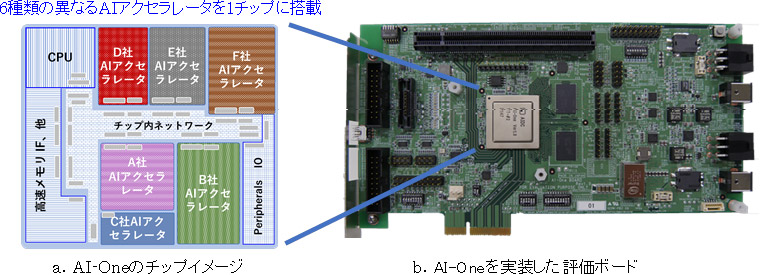

図1 AIアクセラレータ向け評価プラットフォームの実証チップAI-One

目覚ましく進展するIoT社会において、実世界のビッグデータから人々の生活に新たな価値を創造する鍵として人工知能(AI)技術が注目されています。一方、AI技術の根幹をなす半導体集積回路の開発では、微細化が物理的な限界に近づいていること、エネルギー消費が増大し続けていることが極めて大きな課題となっています。この課題を解決するためには、省エネルギーで効率的にAIを動作させる半導体集積回路・デバイス(AIチップ)の開発が必要不可欠であり、世界的にもAIチップの開発競争が激化しています。

日本国内では、多くの中小・ベンチャー企業などが台頭し、AIチップの開発に名乗りを上げています。しかし、AIチップの開発には、半導体を設計するための高度な技術が求められるとともに、高額な回路設計ツールや検証装置などをそろえる必要があり、中小・ベンチャー企業などが自らのアイデアをチップ化する際の大きな障壁となっています。

このような背景のもと、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)は、「AIチップ開発加速のためのイノベーション推進事業※1」において、国立研究開発法人産業技術総合研究所(産総研)、国立大学法人東京大学(東京大学)と共同で、東京大学浅野キャンパス(東京都文京区)内の武田先端知ビルにAIチップ設計拠点(https://www.ai-chip-design-center.org/)を設置し、半導体設計に必要な共通基盤技術の開発や回路設計用のEDAツール※2、標準IPコア※3などからなる設計環境の整備を進めています。

この一環として本AIチップ設計拠点では、アルゴリズムを実行するエンジンとして中小・ベンチャー企業などが開発する独自のAIアクセラレータ※4向け評価プラットフォーム※5の構築※6を進めています。AIアクセラレータを実環境で評価するには、AIアクセラレータと標準システム回路を有するSoC※7、いわゆるAIチップを開発し、それを用いてシステムレベルでの評価が必要なため、多くのコストと時間がかかっています。そこで、本評価プラットフォームでは、共通基盤技術として標準システム回路や検証回路、テスト回路、評価ボードなどを開発し、中小・ベンチャー企業などにこれら共通技術をAIアクセラレータ向け評価プラットフォームとして提供することで、各企業独自のAIアクセラレータ搭載チップの開発とそれを用いたシステムレベルでの評価を短期間に実現することを目指しています。

このたび本評価プラットフォームの実証に向け、中小・ベンチャー企業の協力※8を得て6種類の独自AIアクセラレータを搭載したCMOS※928nmプロセスを用いる実証チップ(AI-One)を設計し、外部の製造会社で試作した実チップの組み立てと評価ボードへの実装を完了するとともに、この評価ボードを用いたチップの評価を開始しました。現在、各協力会社で自身のAIアクセラレータの評価を開始しており、これまでに6種類全てが設計通りの周波数で動作することを確認しました。

なおAIチップ設計拠点では、2022年3月25日に開催する第33回AIチップ設計拠点フォーラムで、AI-Oneの実チップおよび評価ボードの展示や、AIアクセラレータの評価結果などについて紹介します。AIチップ設計拠点フォーラムの詳細については、下記をご参照ください。

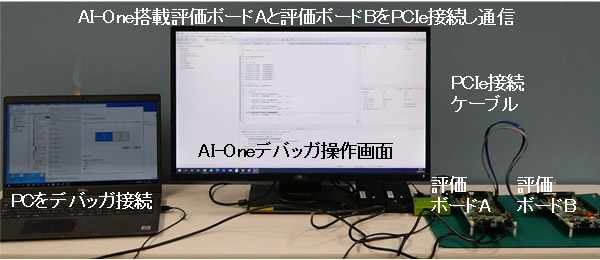

本評価プラットフォームの実証チップAI-Oneの評価として、SoCの動作確認として一般に行われている方法と同様に、今回の評価用に準備した専用の評価ボードにAI-Oneを実装しました。これを用いて、中小・ベンチャー各社のAIアクセラレータの性能確認前に必要な、以下のSoCの基本動作評価を行い、設計通りAI-Oneが動作することを確認しました(図2)。

(1)AI-Oneに組み込んだCPUの800MHz動作において、各AIアクセラレータからLPDDR4※10メモリへ、設計通りのフルバンド幅(24.8GB/s)でのデータ転送を確認しました。

(2)CPUからLPDDR4メモリへ、SoC評価時に求められる安定した読み書き動作(上記バンド幅での室温下8時間の動作)を確認しました。

(3)設計時に各種検証項目で確認した機能・性能(PCIe Gen3※11プロトコル※12 8Gbpsでの通信とプログラム制御、基板上のFLASHに書き込んだプログラムからQSPI※13 25MHzでのブートとLPDDR4の起動、DFT※14機能による内蔵メモリ・ロジック回路・PLL※15の動作、CPUから各AIアクセラレータのレジスタアクセスと割り込み、クロック周波数変更時のAIアクセラレータ動作)が、設計通り動作することを実測しました。

図2 AI-Oneを実装した評価ボードのPCIe Gen3での接続テストの様子

各協力会社は本事業で設計して試作した実証チップAI-Oneを用いて、設計段階で見積もった各AIアクセラレータの消費電力や性能などについて比較評価を行い、さらに詳細な評価を進めます。NEDOと産総研、東京大学はその評価からのフィードバックを活用し、今後さらに使いやすいエッジ向けAIチップの評価プラットフォームを確立していきます。本評価プラットフォームの確立により、AIアクセラレータ以外の部品などを共通部分として提供可能になり、チップ全体の設計や時間が短縮できるため、AIチップを短期間(従来比45%以下)で低コストに開発することができます。

また本AIチップ設計拠点では、AIチップ設計に関する共通基盤技術などの開発を進め、さらに使いやすいAIチップ設計環境を構築していきます。これらの取り組みにより、AIチップ設計拠点の確立と、日本の中小・ベンチャー企業などのAIチップ開発を後押しします。