国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)先進パワーエレクトロニクス研究センター【研究センター長 奥村 元】SiCデバイスプロセスチーム 原田 信介 研究チーム長らは、富士電機株式会社、住友電気工業株式会社、トヨタ自動車株式会社、株式会社東芝、三菱電機株式会社との共同研究で、炭化ケイ素(SiC)半導体を用いた1.2 kV耐電圧(耐圧)クラスの縦型スーパージャンクション(SJ)MOSFETを開発し、SiCトランジスタの世界最小オン抵抗を達成した。また、開発したSJ-MOSFETは、実使用上重要な高温特性や動特性に優れていることを実証した。

n型ピラーとp型ピラーの繰り返しからなるSJ構造はシリコン(Si)トランジスタではオン抵抗の低減効果が実証されているが、SiCトランジスタへの適用はSJ構造の作製が困難なため進んでいなかった。今回、産総研独自のSiCトランジスタの作製技術を応用してSJ構造を狭いピッチで制御良く形成することができた。これによりピッチが狭くオン抵抗が低いSJ構造のトレンチゲート型MOSFETが実現でき、1.2 kV耐圧クラスのSiC-MOSFETのオン抵抗を大幅に低減できた。今後SiCの適用が期待される電気自動車の電力システムの一層の小型化・高効率化や、新たな電力システムの創出への貢献が期待される。

この成果の詳細は、米国サンフランシスコで開催される国際会議IEDM 2018(IEEE International Electron Devices Meeting)にて2018年12月3日(米国太平洋標準時間)に発表された。

|

|

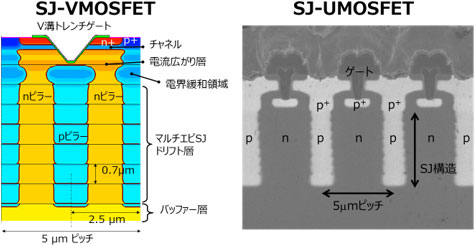

今回開発した2タイプのSiCトレンチゲート型SJ-MOSFET |

エネルギーの有効利用を促進し低炭素社会の実現を目指していくには、電力の変換(直流・交流変換や電圧変換)や制御を担うパワーエレクトロニクス技術を進展させ、パワーエレクトロニクス電力機器を飛躍的に高効率化、小型軽量化、高機能化することが求められている。これらはパワー半導体デバイス(パワーデバイス)の性能に大きく依存するが、既存のSiパワーデバイスはSiの物性から決まる理論限界に近づきつつある。

SiCは、パワーデバイスの小型化や高効率化に有利な物性をもつため、次世代型パワーデバイスの有望な材料として期待されている。近年では、SiCパワーデバイスを搭載した機器が実用化され始め、研究フェーズはさらなる性能向上を目指して、次世代型パワーデバイス構造の開発に移行しつつある。

産総研は、パワーエレクトロニクスをオープンイノベーション拠点TIAの戦略的研究領域の一つと位置付け、SiCパワーデバイスの量産試作ラインの整備とともに、民活型共同研究体「つくばパワーエレクトロニクスコンステレーション(TPEC)」を発足させ、SiCパワーデバイスの量産試作技術開発に関する共同研究を推進してきた。これまで、富士電機株式会社との共同研究で、プレーナーゲート型MOSFETのIE-MOSFETとトレンチゲート型MOSFETのIE-UMOSFETを開発し量産試作を実証してきた。住友電気工業株式会社との共同研究では、住友電気工業株式会社が開発したトレンチゲート型MOSFETであるVMOSFETの量産試作を実証してきた。

今回、ハイブリッド電気自動車/電気自動車の電力変換システムでの使用が期待される1.2 kV耐圧クラスデバイスの超低オン抵抗化を目指し、トレンチゲート型SJ-MOSFETの開発に富士電機株式会社、住友電気工業株式会社、トヨタ自動車株式会社、株式会社東芝、三菱電機株式会社とともに取り組んだ。

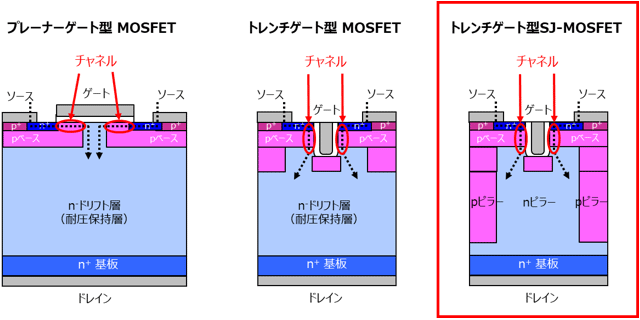

図1に各種SiC-MOSFETの断面構造を示す。プレーナーゲート型MOSFETのオン抵抗はゲート酸化膜と半導体の界面(MOS界面)の欠陥による大きなチャネル抵抗に支配されており、セルピッチを狭めてチャネル密度を増大する構造設計やMOS界面の欠陥を低減するプロセス開発に注力されてきた。近年、トレンチゲート型MOSFETが実現して、低いオン抵抗が達成されたため、さらなるオン抵抗低減には耐圧保持層となるドリフト層をSJ構造とすることが、Siパワーデバイスの実績から有効と期待されていた。

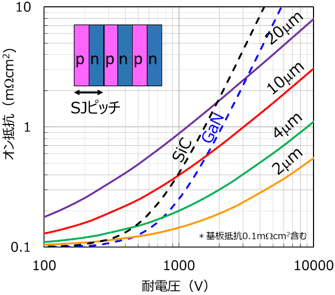

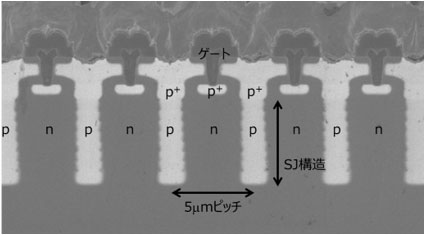

SJ構造はドリフト層をn型とp型のピラーで構成し、図2に示すようにピッチ間隔を狭くするとSiCや窒化ガリウム(GaN)の縦型デバイスの理論限界以下に抵抗を低減できる。特に1.2 kV耐圧クラスでは、数µm程度のピッチでSJ構造により縦型デバイスの理論限界以下の抵抗となる。しかし、SiCは非常に硬いためSiのように容易に加工できず、狭いピッチのSJ構造を作製するのは困難であった。産総研にはイオン注入とエピタキシャル成長を組み合わせたSiCトランジスタの独自構造であるIE-MOSFETの開発で得たノウハウがある。今回、n型エピタキシャル成長とp型イオン注入を繰り返してピラーを積み上げていくマルチエピタキシャル法に、このノウハウを応用することで狭いピッチのSJ構造を精度良く形成できた。図3に作製したトレンチゲート型SJ-MOSFET(SJ-UMOSFET)の断面写真を示す。MOSFETのp型領域と繋がるように、8段の多層膜からなるp型ピラーが、横方向にズレなく垂直に形成されているのが分かる。

|

|

図1 縦型SiC MOSFETの構造の種類(赤く囲んだMOSFETが今回開発したSJ-MOSFET) |

|

|

図2 従来のSiCとGaNの縦型デバイス(点線)、ピッチの異なるSiCの縦型SJデバイス(実線)に対する耐電圧-オン抵抗の理論限界線 |

|

|

図3 今回開発したトレンチゲート型SJ-MOSFET (SJ-UMOSFET)の断面写真 |

次に、今回開発したSJ構造のMOSFETを既存のトレンチゲート型MOSFETと組み合わせ、実使用を想定して、さまざまな評価を行い、1.2 kV耐圧クラスのトレンチゲート型SJ-MOSFETの製品化の可能性を検証した。

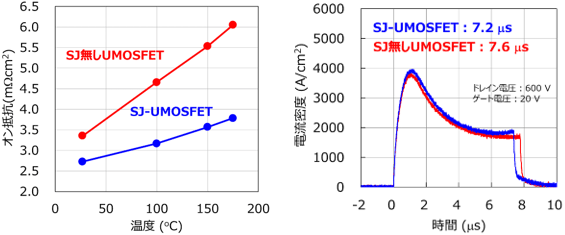

まず、4インチウエハー全面で1.2 kV耐圧クラス(耐圧1400 V以上)が得られる量産レベルの設計のMOSFETの高温特性と動特性を評価した。IE-UMOSFETの室温と175 ℃のオン抵抗をSJ構造の有無で比較すると、室温での差は0.7 mΩcm2と小さいが、175 ℃ではSJ構造無しの6 mΩcm2に対しSJ構造有りでは3.8 mΩcm2と低く抑えられていた(図4左)。この結果から、SJ-UMOSFETは高出力で動作しても自己発熱によるオン抵抗の増加が少ないことが分かる。また、モーターなどの負荷が事故などで短絡した際、通電状態のままデバイスに高電圧がかかって破壊に至るまでの時間を表す負荷短絡耐量は、SJ構造の有無にかかわらずほぼ同等で、SJ構造による安全性の低下は見られなかった(図4右)。

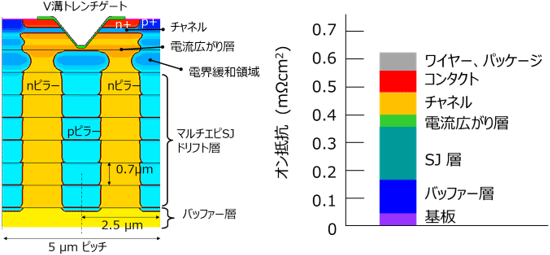

次いでSJ構造によるオン抵抗低減効果を検証した。図5に作製したSJ-VMOSFETの断面構造とオン抵抗の内訳を示す。VMOSFETはMOS界面欠陥が少ない(0-33-8)結晶面をチャネルにしたため、チャネル移動度が高いトレンチゲート型MOSFETである。今回、狭いピッチのSJ構造が作製できるようになったため、SJ構造に合わせてMOSFETセルピッチを大きくする必要がなく、低オン抵抗に最適化できた。狭いピッチのSJ構造と低オン抵抗MOSFETの両方の効果によって耐圧1170 Vでオン抵抗0.63 mΩcm2という同耐圧レベルのSiC-MOSFETでは世界最小オン抵抗を達成できた。

以上のように、比較的低い耐圧である1.2 kV耐圧クラスでSiC-MOSFETへのSJ構造適用が有効であることが明らかとなった。

|

|

図4 SJ-UMOSFETとSJ無しUMOSFET(IE-UMOSFET)のオン抵抗の温度依存性(左)と負荷短絡耐量(右) |

|

|

図5 今回開発したSJ-VMOSFETの断面構造とオン抵抗の内訳 |

今後は、企業への技術移転を念頭に、企業連携をさらに強化し、SJ構造の設計と製造プロセスの高度化を進め、信頼性や耐量など実使用を想定してデバイス特性の向上を図る。