独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】ナノスケール計測・プロセス技術研究グループ 多田 哲也 研究グループ長、福田 浩一 主任研究員は、微細トランジスタの不純物濃度分布を高精度で測定するための走査トンネル顕微鏡(STM;Scanning Tunneling Microscope)シミュレーション技術を開発した。

STMは、半導体試料表面の静電ポテンシャルや半導体内のキャリア濃度を反映するトンネル電流を測定できるため、微細トランジスタのドーパント不純物濃度分布測定への活用が期待される。しかし、STMは測定に際し試料に電圧をかけるため、その電圧や、それによって試料内部を流れる電流が、試料のポテンシャル分布を変化させてしまって正確なポテンシャル分布を測定できないという問題があった。従って、正しいポテンシャル分布を得るために、その影響を取り除く必要があった。今回開発したシミュレーション技術では、STM探針と半導体試料の間に電圧をかけた時の影響、特に探針と試料の間に流れるトンネル電流が試料内部にも流れる影響を計算機シミュレーションにより取り除ける。この技術により、STMを用いてポテンシャルや不純物濃度の分布の高精度測定ができるようになった。これまで難しかったナノメーターレベルの正確な測定が可能となることから、次世代トランジスタの開発への貢献が期待される。

なお、この技術の詳細は、近日中に、米国物理学協会の科学雑誌Journal of Applied Physicsに掲載予定である。

|

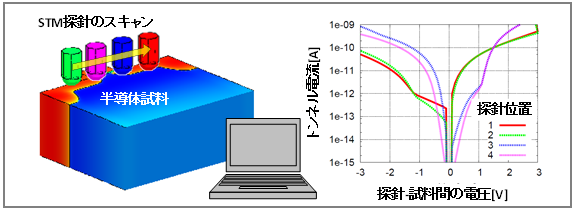

半導体試料のSTM測定の計算機シミュレーション

探針と半導体試料を含めた計算により探針位置の不純物濃度に応じた電流が得られる。 |

近年の大規模集積回路(LSI)の発展に伴って、そこで使われるトランジスタの微細化は限界に迫ろうとしており、不純物ドーパントの高精度制御が必要とされている。それには高い空間分解能で不純物濃度分布を測定することが不可欠で、STMは非破壊で高い空間分解能で測定できる手法として注目を浴びてきた。図1に半導体試料のSTM測定の概念図を示す。半導体試料とSTM探針の間に電圧をかけると、探針直下の試料表面の静電ポテンシャルとキャリア濃度に依存してトンネル電流が流れる。STMは探針でスキャン(走査)するので、各位置の不純物濃度を反映しているトンネル電流からn型・p型の不純物濃度分布を測定できると期待された。

しかし、STM探針と試料の間に電圧をかけるため、与えた電圧やトンネル電流が試料内に流れる影響で、探針直下の静電ポテンシャルやキャリア濃度が変化するため、実際の不純物濃度の情報は得られない。この影響を取り除くにはSTMの計算機シミュレーションが必要とされていたが、これまで原子スケールで原理的に解くSTMシミュレーションは提案されていたものの、半導体試料内を電流が広範に流れる影響を解析できる計算機シミュレーション技術はなかった。

|

|

図1 半導体試料のSTM測定の概念図 |

|

トンネル電流はn型・p型など、探針直下の不純物濃度を反映しているため、左図の各点での電流電圧特性は、右図のようにその位置の不純物濃度によって異なる。 |

産総研ナノエレクトロニクス研究部門ナノスケール計測・プロセス技術研究グループは、微細半導体デバイスの物理解析を高精度化するために、計算機シミュレーションのTCAD技術を援用し、ナノメートルの精度で物理量を測定する手法の開発に取り組んできた。

今回、測定値との差の原因を一つ一つ想定して、重要な因子を絞り込んでいく研究方法によりSTMの測定をできるだけ正確に再現・解析できる計算機シミュレーション技術の開発に取り組んだ。

今回開発したSTMシミュレーターは、半導体試料とSTM探針の構造を半導体製造プロセスシミュレーションによって構築し、STMの測定条件を入力すると、試料と探針の間の距離の自動調整や探針の走査などのSTMの測定手順を自動的に再現し、半導体デバイスシミュレーションによって測定されるトンネル電流電圧特性を予測する。

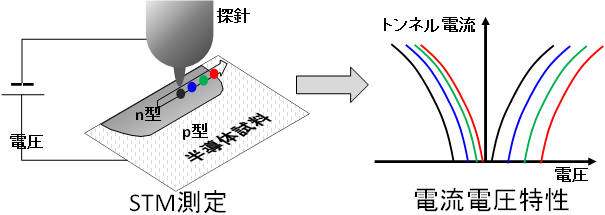

図2にシミュレーションの電流計算の概念図を示す。半導体デバイスシミュレーション技術を取り入れたことで、試料と探針の間に流れるトンネル電流と、半導体内部に流れる電子・正孔電流を矛盾なく計算できるようになった。

|

|

図2 シミュレーションの電流計算の概念図 |

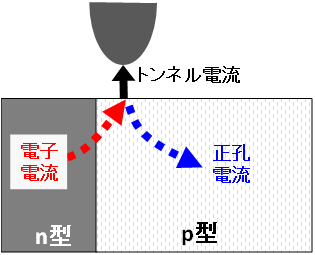

図3に不純物濃度が既知の半導体試料をSTMで測定した電流電圧特性(マーカー●で表示)と今回開発したシミュレーターによる予測値(実線で表示)を示す。半導体内部の電流の影響を考慮することで、半導体試料の測定値を精度よく計算できることが初めて検証された。

|

図3 STMで測定した半導体試料の電流電圧特性(点)とシミュレーション結果(実線)

シミュレーションは測定結果を精度よく再現している(3x10-13[A]以下はSTMの測定限界)。

なお、点線は電流の広がりを無視したシミュレーション結果で、測定値と合わない。 |

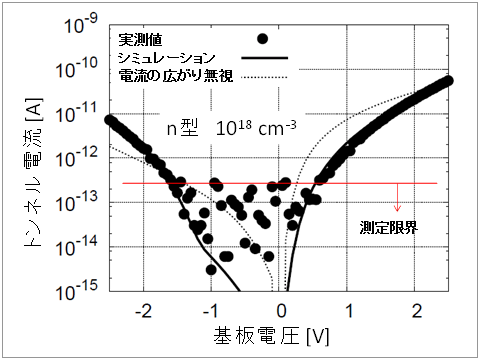

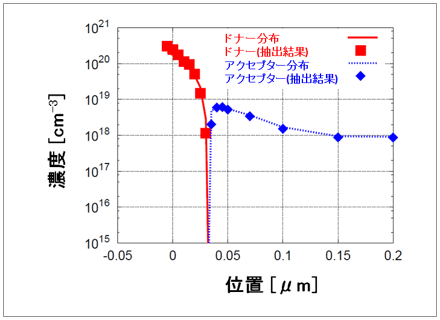

図4に今回開発した技術を用いて不純物分布を推定するテストを計算機上で行った結果を示す。半導体製造プロセスシミュレーションでn+p接合の不純物濃度分布(線で表示)を想定し、今回開発したシミュレーターで、そのSTM測定結果を予測した。予測したSTM測定結果から、今回のシミュレーション技術で逆に濃度分布を求めて、はじめに想定した濃度分布と比較した。想定した不純物分布とは異なる不純物分布の初期値から開始して推定した濃度分布がマーカーで示してある。推定した濃度分布ははじめに想定した不純物濃度分布と、0.01 µm(10 nm)の精度でよく一致している。このように今回開発したシミュレーターを用いれば、STMの測定で半導体試料の不純物分布を高精度に推定できる。

|

|

図4 n+p接合の不純物分布推定テスト結果 |

今回開発したSTMシミュレーション技術を半導体デバイスの開発者に提供し、微細デバイスの実現を加速させるとともに、STMの測定者に提供し、測定手法の向上に寄与する。さらに、つくばイノベーションアリーナ ナノテクノロジー拠点(TIA-nano)や産総研スーパークリーンルーム(SCR)産学官連携研究棟で、産業界と大学が一体となって次世代技術の研究を進めるための共用インフラとして活用する。