日本原子力研究所(理事長 岡_ 俊雄)(以下「原研」)と独立行政法人 産業技術総合研究所(理事長 吉川 弘之)(以下「産総研」)は共同で、炭化ケイ素半導体を基板としたトランジスタ(半導体素子)を開発し、性能指標であるチャンネル移動度(電子の動き易さ)について、実用化に必要な壁200cm2/Vsを破り、230 cm2/Vsという世界最高性能を達成した。

炭化ケイ素(SiC)半導体によって、従来のシリコン(Si)半導体を凌駕する小型で電力損失が少ない半導体素子を実現することが可能であり、電力、鉄道、家電などの様々な分野で電力制御用素子としての応用や、宇宙・原子力施設で使用する放射線に強い半導体素子への応用が期待されている。SiCは、Siと炭素(C)元素から構成され、元素の繰り返し配列のパターンが異なる結晶型が多数存在する。その中で、立方晶の単結晶は、電気的特性が最も優れているものの、高品質結晶の育成が困難であり、結晶成長技術の開発が求められていた。これに加え、SiC素子の製作に当たっては、pn接合形成に不可欠な電気伝導型の制御と良質の絶縁膜形成の技術開発が素子実現の鍵となっていた。

原研及び産総研では、SiC基板上への高品質な単結晶の育成技術を産総研で、トランジスタ製作技術の開発を原研で分担する共同研究を平成14年7月から進め、これらの課題克服に取り組んだ。この結果、産総研は、立方晶SiC基板(HOYAアドバンテストセミコンダクタ(株)提供)の上に、原料ガスを熱分解して成分元素を基板上に堆積させる化学気相成長法を用いて条件の最適化を進め、高品質のp型立方晶膜を成長させることに成功した。原研は、これまで培ってきた知見を活かし、その単結晶膜に高温でのイオン注入によって不純物(リン)を添加して部分的にn型領域を作り、水素を燃焼させながら行う酸化技術により良質の絶縁酸化膜を形成することで懸案の技術的課題を解決し、高性能の電界効果トランジスタ(MOSFET)の製作に成功した。

トランジスタの性能指標であるチャンネル移動度は、実用化の目安である200 cm2/Vsを超え、世界最高の230 cm2/Vsに達した。立方晶SiCを基板とした半導体素子は、数kV級以上の超高電圧制御には適さないが、最も市場規模の大きい数百V級の家電製品には最適であり、当該素子が実用化されると極めて大きな省エネルギー効果や放射線に強いことから、宇宙・原子力産業への多大な貢献が期待できる。今後は、実用化に向けて、結晶の品質向上、チャンネル移動度向上をさらに進めるとともに、懸案となっているMOSFET駆動に必要な最低電圧「しきい値電圧」の制御技術と絶縁酸化膜の信頼性向上技術の確立を目指していく予定である。

○炭化ケイ素(SiC)半導体素子開発のねらい

現在製造されている半導体素子はシリコン(Si)を材料としたものが中心であり、Si半導体素子が様々な分野や環境で使用され、我々の暮らしを確実に豊かにしてきた。しかしこのことは、一方で、これまで半導体が使用できないと考えられていた厳しい条件や環境でも半導体素子を使用し、高度な機器制御や情報・エネルギー伝達を行いたいというさらなる要求を産んでいる。実際、高温や高電圧、高放射線場といったSiの物性限界を超える環境下でも使用可能な半導体素子を開発することが近年求められるようになってきた。

例えば、発電所・変電所での電力変換から始まり家電製品のインバータとしてまで幅広い範囲で使用されるようになってきている電力変換用パワー素子においては、省エネルギーの観点から、より小型・低損失・高効率化が求められており、これにもSiを凌駕する半導体材料を用いた素子の開発が必要となっている。また、今後、さらなる高性能・高信頼性化が必要となる通信用の高周波素子、さらには、人工衛星等で使用される耐放射線性半導体素子に関してもSi素子の限界を越える性能を持つ素子開発が必要となっている。

炭化ケイ素(SiC)は、Siに比べ絶縁破壊電界が一桁以上大きく、熱伝導がSiの三倍良く、耐熱性・耐薬品性に優れるだけでなく、放射線に対する耐性がSi素子より二桁高いといった優れた性質を持つ。従って従来のSi半導体素子よりはるかに小型、低損失、高効率のパワー素子、高周波素子や耐放射線性の半導体素子が作製可能である。このことからSiCは、超低損失の電力変換素子、高性能・高信頼性化が一層必要となる携帯電話の基地局等で使用される高周波素子、さらには、過酷な環境下で高い信頼性が要求される宇宙や原子力施設で使用される耐放射線性素子用の半導体材料として期待が大きい。

○開発の問題点と達成内容

SiC半導体の実用化のための技術的課題は大別して二つあった。極めて良質なSiC単結晶の育成技術とSiC単結晶を素子に加工するための技術(素子化プロセス技術)の確立である。原研と産総研は共同で、これらの課題を解決するための研究を推進した。

SiCは、Siと炭素(C)原子から構成されるが、原子の繰り返し配列のパターンが異なる結晶型が多数存在する。その中で、代表的なものが、図1に示すような立方晶と六方晶である。このような結晶型の違いにより物理的性質や電気的性質は異なり、立方晶SiCは六方晶SiCよりバンドギャップが少し狭いが電子の移動度(電子が走る速さ)は大きいのが特徴である。バンドギャップが広い方がより高い電圧に耐える性質を持つが、一方電子移動度が大きいものは高速動作が可能となる。このため、バンドギャップの広い六方晶SiCは発電所などで用いる数kV級以上の超高電圧用素子として有望視され、立方晶SiCは高速動作が要求される数百V級の家電製品用素子には最適な材料とされている。さらに、立方晶SiCは、六方晶をはじめとする他の結晶型とは異なり、電気特性が結晶方位(原子配列の方向)に依存せず、素子製作に最適な材料と見なされている。しかし、高温で容易に単結晶が作れる六方晶とは違い、立方晶SiCは高品質の単結晶育成が極めて困難であった。このため、六方晶の構造を有する単結晶基板のみが製造され、市販されているのが実情であった。しかし、市販の基板には結晶中に原子配列の不整合や貫通孔(ピンホール)などの欠陥が多く存在することから、素子を製作するとこれらの欠陥が原因となり漏電等の不具合が発生すると考えられ、大きな問題となっていた。

立方晶SiC |

六方晶SiC |

|

図1 SiC結晶型の例

|

これらの問題を克服するため、これまでSi基板の上に、シラン、プロパン等の原料ガスを熱分解して成分元素を基板上に堆積させる化学気相成長(CVD)法を用いて立方晶SiC膜を合成してきた実験室レベルの実績を発展させ、立方晶SiC基板自体を種結晶として高温で同型SiCの結晶成長を行うことを検討した。この時問題となるのは適切な種結晶基板の入手であった。これまで実験室レベルでは、Si基板上に成長できるSiC膜の厚さは約0.03ミリメートルが最高であり、薄く割れやすいことから種結晶基板には不適であった。これに対し、近年6インチ径のSi基板を用いて大面積で厚い立方晶SiC(厚さ0.2ミリメートル程度)を成長させる技術をHOYAアドバンテストセミコンダクタ(株)が開発したことを受け、Si基板をエッチングにより除去し、残った立方晶SiCのみを種結晶基板として使用することを考案した。これを基に産総研は、従来のSi基板上への立方晶SiC成長では不可能であったSiの融点(1400℃)以上での温度領域で、CVD法による結晶育成技術の開発を進め、1600℃の高温条件で素子製作に適合する高品質なp型立方晶SiC単結晶膜の成長に成功した。

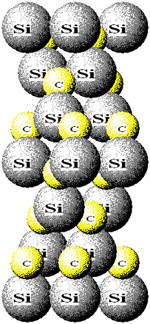

一方、SiC半導体の素子化プロセス技術では、不純物導入によるp型、n型の電気伝導型制御と酸化による良質の絶縁膜形成の技術開発が素子実現の鍵となっており、原研はこの課題解決に取り組んだ。SiC素子としては、集積回路の基本要素構造である金属-酸化膜-半導体(MOS)電界効果トランジスタ(FET)(図2に模式図)に着目して、その開発を進めた。MOSFETの動作原理は、ゲートに電圧を加えることでソースとドレイン間に「チャンネル」と呼ばれる電子の通り道を形成し、その通り道の幅を変えることで流れる電流を制御するものである。チャンネルを流れる電子の移動度(チャンネル移動度)が大きい方が性能は良いとされる。このためにまず必要なのが、低抵抗のn型ソース、ドレイン部の形成である。この低抵抗n型層形成のため、原研でこれまで六方晶SiCを対象に開発を行ってきた高温イオン注入技術を適用した。

|

|

図2 SiC MOSFET模式図(断面)及び顕微鏡写真

|

n型SiCの形成には、リン(P)等のV族元素不純物をSiCに添加する必要があるが、これらの不純物の熱拡散係数は極めて小さく、Si素子製造で従来から使われている熱拡散法ではSiC内に導入できない。不純物をイオン化して外部から強制的に導入するイオン注入法が有望視されるが、低抵抗層の形成には多量の不純物添加が必要であり、従来どおり室温でイオン注入すると注入領域の結晶配列がばらばらに乱れ、所謂アモルファス層が形成される。一旦アモルファス化すると、立方晶SiCの結晶性を回復させるのは非常に難しく、注入層は高抵抗のままとなり、素子が作れない。この課題を解決するため、SiC結晶を高温にしてイオン注入を行う高温イオン注入技術を活用した。Pイオンを800℃である程度の結晶性を保たせたまま立方晶SiCに注入し、その後1650℃で残留欠陥を除去することで、トランジスタ動作に適合する低抵抗n型ソース、ドレイン部が形成できた。

次に挑戦したのが、良質の酸化絶縁膜の形成である。SiCは酸素(O)ガス中で加熱すると酸化膜(SiO2)を形成できるが、Si素子で適用されている乾燥酸素による酸化などではMOSFETのゲート部の良好な絶縁膜が形成できず、トランジスタ性能としては本来SiCが持つ物性から予測されるチャンネル移動度の1/10程度に止まり、大きな障壁となってきた。この要因は、ゲート酸化膜と半導体の界面に存在する欠陥(界面準位)であり、これがチャンネル内の電子を散乱することで移動度を低下させていることを突き止め、界面準位を水素原子で終端して(水素原子を結合させて)その影響を低減することを発案し、水素を燃焼させながらSiCを酸化させる技術を編み出した。これにより、高品質のゲート酸化絶縁膜が形成できるようになり、トランジスタ性能の向上につながった。

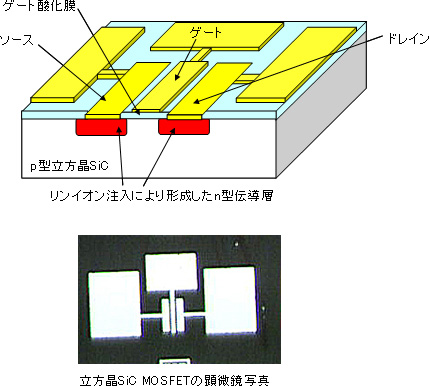

産総研で製作した立方晶SiC単結晶に、原研で開発した高温イオン注入や水素燃焼酸化技術を適用することで(図3に素子作製工程を模式的に示す)、高性能MOSFETの作製に成功し、性能指標であるチャンネル移動度230 cm2/Vsという実用可能レベルの値を世界で初めて達成できた。

|

|

図3 MOSFETの作製工程

|

優れた物性を有するSiCはSiを越える小型、低損失、高効率なパワー素子や高周波素子、耐放射線性素子への応用が期待されながらも、これまで試作されてきたMOSFETでは基本特性の一つであるチャンネル移動度が低く、実用化への大きな障壁となっていたが、今回の成果はそれを確実に打ち破った。産総研が開発したCVD法による立方晶SiC単結晶の作製技術は、高いチャンネル移動度を持つMOSFETを得るための高品質な基板作製への重要な知見となり、今後、実用化に際して不可欠となる高品質基板を安定・大量供給する際に大いに役立つ。また、原研が、実用化の目安である200cm2/Vs以上のチャンネル移動度を持つMOSFETの試作に成功したことは、立方晶SiCを用いた数百V級電力素子や耐放射線性素子の実用化に向けた最大の課題をクリアしたことになる。最も市場規模の大きい数百V級の家電製品(エアコン、電子レンジ、冷蔵庫、洗濯機、炊飯器等)用に当該デバイスが実用化されると極めて大きな省エネルギー効果が期待でき、さらに宇宙産業や原子力産業に多大な貢献が期待できる。

今後はSiC素子の実用化へ向け、更なる立方晶膜結晶品質の向上、プロセス技術の最適化によるチャンネル移動度の向上に加え、懸案となっているMOSFET駆動に必要な最低電圧「しきい値電圧」の制御技術の確立、酸化膜の耐電圧向上及び高温・高電圧下での絶縁特性の長期安定性といった信頼性の向上に関する技術の確立を目指していく予定である。