独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)は、半導体素子の微細化・高性能化を追究すると共に、微細化限界を超える新コンセプト技術の創出を目的とする「ナノ電子デバイス研究センター【研究センター長 金山 敏彦】(以下「研究センター」という)」を平成20年4月1日に設立しました。

半導体集積システムは、高度情報社会を支える基幹技術であり、産業競争力の向上と環境負荷の低減を図り、社会の持続的な発展を実現するためには、半導体技術の発展が滞ることは許されません。

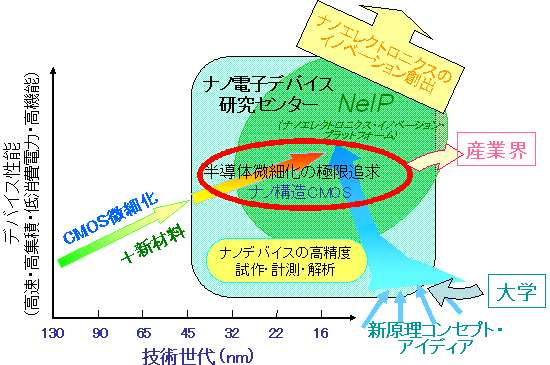

半導体技術の高度化のためには、ナノレベルの微細化と同時に、新規な材料・構造・作製プロセスの導入が必要です。さらに、今後10年以上に亘って発展を継続するには、CMOSトランジスタの微細化に代わる新しい指導原理を構築しなければなりません。研究センターは、32 nmあるいは22 nm技術世代への半導体素子の微細化・高性能化の極限追究を推進すると共に、産総研内外の幅広い科学的知見を動員してより微細な技術世代を実現するための新コンセプト技術を創出するために ナノエレクトロニクス イノベーション プラットフォーム(NeIP)を整備して、イノベーションハブとして機能することを目指します。

|

|

電子素子の微細化・高性能化の極限追究とイノベーションハブとしてのNeIP

|

これまで半導体技術の高度化を担ってきたシリコンCMOSトランジスタの微細化は物理的・技術的な限界に近づいてきています。この限界を打破して32nm以降の技術世代を実現するためには、ナノレベルの微細化と同時に、新しい材料、構造、作製プロセスを導入することが必要となります。さらに、2020年ごろにはそれも限界に近づき、さらなる発展を図るには、これまでのCMOS微細化に代わる新しい原理に基づくデバイス技術を開発する必要があると考えられています。これらの要求に応えるには、幅広い科学的知見を動員して新しいコンセプトに基づく技術を創出すると共に、多様な選択肢の中から利用目的に即した的確な技術選択を行い、産業界と協力して速やかに量産技術に展開できるような研究開発体制を築く必要があります。

このような方向性のナノエレクトロニクスの研究を産総研のような公的研究機関が継続的かつ戦略的に推進することが強く求められています。たとえば産業競争力懇談会(COCN)は、「多様な材料を用いたナノ新デバイスの基礎研究拠点」を設立することを提言しています。また、平成19年度には経済産業省、文部科学省、科学技術振興機構(JST)が連携してナノエレクトロニクス関連のプロジェクトを開始しました。デバイス試作能力を持つ拠点を形成していくことが検討されています。

産総研では、これまで、スーパークリーンルーム産学官連携研究棟を主な拠点として、半導体MIRAIプロジェクトを、次世代半導体研究センター(平成20年3月終了)が中心的な役割を果たしながら、産業界や大学と共同で推進し、半導体の微細化技術の研究開発を行ってきました。MIRAIプロジェクトは、ひずみシリコン技術や高誘電率ゲート絶縁膜技術など、これまでのCMOSトランジスタの構造を維持しながら特性を高度化させる技術について、大きな成果を上げてきました。しかし、CMOSトランジスタの寸法が10 nmという原子レベルに近づくに従い、ますます幅広い技術選択肢に挑戦することが必要になり、ナノエレクトロニクスと呼ばれる、半導体以外の技術分野を包含する研究開発が重要になっています。このような状況を受けて、産総研は電子デバイス技術の研究開発において、今後も主導的な役割を続けるために新センターを設立しました。

新研究センターはMIRAIプロジェクトで培われた高度な技術を引継ぎ、CMOSの微細化・高性能化の極限追究を推進していきます。そのために、高精度なデバイス試作とその電気的特性評価、ナノレベルの物理計測評価解析、第一原理電子状態計算からデバイスシミュレーションまでを含む計算科学的解析を、総合的に行います。さらに、CMOS微細化に代わる新たな発展軸となりうる革新技術の探索と実証を行うためのイノベーションハブであるNeIP(ナノエレクトロニクスイノベーションプラットフォーム)を整え、産総研の他部門や外部機関と連携して基礎技術をデバイス実証に結びつける場として運用して行きます。そこでは、CMOS技術をベースに、新材料・新構造デバイスを効率的に試作し、測定データやシミュレーション結果が体系的に蓄積されるような、知識マネージメントを行います。

CMOSの極限追究を目的とするプロジェクト研究を進めると共に、センターに蓄積されたナノ電子デバイスの作製技術・計測解析技術を基にNeIP(ナノエレクトロニクス イノベーション プラットフォーム)を稼働させ、産総研内外の研究機関と連携して、ナノエレクトロニクスの新原理技術の研究開発を行います。