独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノテクノロジー研究部門【研究部門長 南 信次】ナノシミュレーション研究グループ【研究グループ長 米谷 慎】森田 裕史 主任研究員は、高分子の粗視化モデル(散逸分子動力学法)を用いて、半導体のリソグラフィーにおけるパターニングプロセスのシミュレーション手法の開発を行い、パターン側壁荒れ(line edge roughness: LER)の生成プロセスを高分子鎖のレベルで再現、可視化する技術を開発した。

半導体リソグラフィーのパターニングプロセスでは、回路をシリコン基板に数十ナノメートル(nm)の幅の線で回路パターンを焼き付ける前に、基板上に感光性の高分子材料(フォトレジスト)を塗布し、回路部分、あるいは回路でない部分に極端紫外光等の光を照射して、光反応によってフォトレジスト薄膜に回路の基を描く。光反応した部分、あるいは逆に未反応の部分を現像液で洗い流して、数十nmの線幅の回路パターンを作成するが、現像の際に、そのフォトレジストのパターン側壁に荒れが生じることが近年問題となっている。プロセスが進行中はパターンの構造を測定できないため、原因究明には、さまざまな条件でパターンを作製し、得られた最終パターン形状からプロセスで生じている現象を推測するのが一般的である。本研究では、パターニングプロセス中に生じている現象を解析するための手法のひとつとして、シミュレーションモデルを開発した。このシミュレーションによって、フォトレジストのパターン側壁の形成プロセスで起こっている現象を高分子鎖のレベルで可視化でき、レジスト材料の研究開発に有用なさまざまな情報を得ることが可能となる。

さまざまなレジストプロセスへの実用化に向けて、パターン生成プロセスにおける高分子鎖のスケールでのメカニズムの解明を目指してさらなる開発を進めている。また、次世代リソグラフィーのパターニングプロセスに対応したフォトレジストの開発への応用も進めている。

|

|

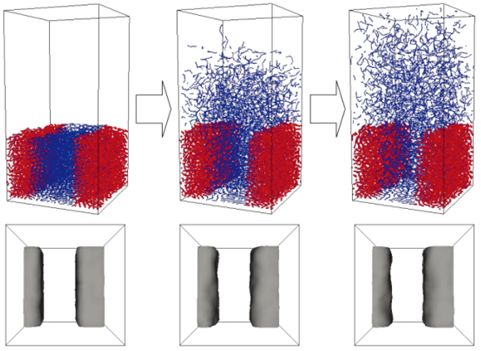

図1 上図:本シミュレーションによって得られたパターニングプロセスのスナップショット。赤の粒子は、パターンとして残るフォトレジストの粒子を、青の粒子は、現像液に溶けるフォトレジストを表す。なお、現像液である溶媒の粒子は表示していない。下図:側壁イメージの測長走査型電子顕微鏡(CDSEM)像をシミュレーションした結果。 |

近年、半導体の高集積化に伴い、パターンの幅が数十nmまで微細になってきている。この微細化により問題となってきたのが、回路パターンの側壁の荒れ(line edge roughness: LER)、もしくはパターン幅の荒れ(line width roughness: LWR)である。現在、盛んに開発が行われている20-35nmのパターンの場合、LERを2nm程度に押さえる必要があることがSemiconductor Industry Association 等が中心となってまとめた、国際半導体技術ロードマップ(International Technology Roadmap for Semiconductors)に示されている。この問題に対して、国内外のフォトレジストメーカーは、露光光源に適合した低LER・低LWRとなる高分子フォトレジストの開発を装置メーカーによるプロセス設計・開発とともに進めている。これらの開発では、回路パターンの側壁の荒れの生成機構の解明が重要であり、そのための研究開発手法が求められている。

ナノメートルスケールでの材料やプロセスの研究開発では、その過程の観察が重要であるが、スケールの問題や動的な変化を伴うなど、実験による観測・測定が困難な場合がある。そこで、そのプロセスの過程を可視化する方法として、シミュレーション技術の研究・開発を行った。

具体的には、リソグラフィーのパターニングプロセスの粗視化シミュレーション手法を開発し、パターン側面荒れの生成過程をシミュレート(仮想実験)する。一連のシミュレーション結果から、低LER・低LWRとなるフォトレジスト材料がもつ要件をプロセスの観点から探索し、材料設計に役立てることを目標とした。

また、高分子であるフォトレジスト材料開発にフィードバックできるように、高分子鎖、すなわち“鎖状分子”を認識できるシミュレーションの開発を進めてきた。

従来、半導体リソグラフィーのパターニングプロセスのシミュレーション手法の多くが、メッシュを用いたモデルであった。今回、高分子鎖を鎖状分子として取り扱える粗視化モデルのひとつである散逸分子動力学法を基にしたモデルを用いてフォトレジストの高分子を表すことによって、パターニングプロセスの過程での、鎖状分子の動的な変化をシミュレーションすることに成功した。

|

|

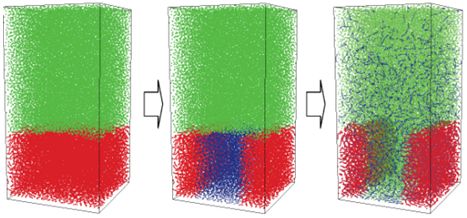

図2 高分子フォトレジスト膜を用いたパターニングプロセスのシミュレーションの概要。左図は初期構造を表す。濃い緑の粒子が気相粒子を、薄い緑の粒子が現像液粒子を、赤の粒子が現像液に溶けないフォトレジストを、青の粒子が現像液に溶けるフォトレジストを表す。 |

初期構造として、図2左に示す構造を作成する。下の赤い層がフォトレジスト膜を、上の濃い緑の粒子が気相を表す。露光によって現像液に溶けるようになったフォトレジストを青の鎖状分子で表し、露光による反応のシミュレーションを行う。現時点では、この過程に光酸発生剤の拡散は取り入れていないが、今後取り入れる予定である。さらに、濃い緑の気相粒子を、薄い緑の現像液粒子に置き換えることにより、現像液中に溶けるフォトレジスト(青)が、鎖状のまま拡散していく様子を計算することができた。

実験では、通常、測長走査型電子顕微鏡を用いて、パターン側壁の荒れ(LER)の定量的な測定が行われるが、その電子顕微鏡像をシミュレートした結果を図1下に示す。このシミュレーションにより、初期構造では側壁の荒れがほとんどないのに対して、溶解過程で荒れが大きくなっていることが可視化できた。

さらに、現像液に溶ける層と溶けない層の間の界面厚が薄い場合と、界面厚が厚い場合について、それぞれシミュレーションしたところ、界面が薄い場合に、側壁の荒れが小さいことが明らかになった。

本研究で開発したリソグラフィーのパターニングプロセスのシミュレーション手法は、ナノメートルスケールでのパターニングプロセスのモデルであり、比較的汎用性が高い。今後は、EUVレジストプロセス、二重露光プロセス、液浸露光プロセス等の最近開発されているリソグラフィー技術への適用を目指して、モデルの拡張等を行っていく。また、個々のフォトレジスト材料について実験データと照合することにより、フォトレジスト材料、プロセス双方に対して、定量的に対応させるための開発を進めたい。また、国内外のフォトレジストメーカー等と連携して、最新技術への応用を目指したい。