NEDOは「AIチップ開発加速のためのイノベーション推進事業」を行っており、本事業において産業技術総合研究所および東京大学と共同で、東京大学本郷地区浅野キャンパス(東京都文京区)内に「AIチップ設計拠点」の整備を進めてきましたが、このたび2023年4月1日に、本拠点の本格運用を開始します。

本拠点では、利用者の計画に応じてフレキシブルに構築できる半導体設計環境や、本事業で開発した「AIチップ向けIPの設計・評価プラットフォーム」などを提供します。

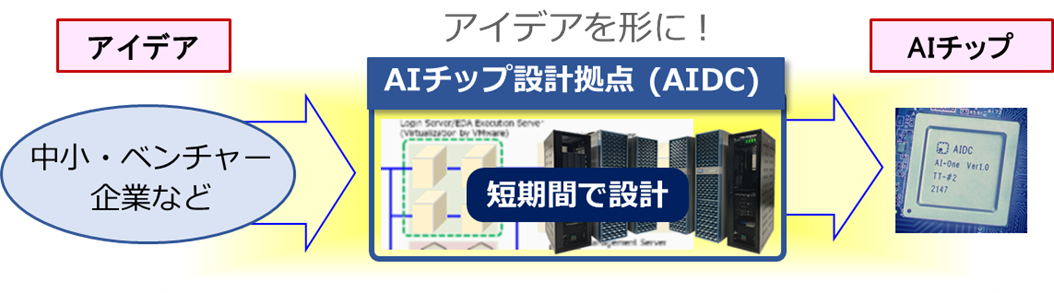

これにより、AIチップの設計からデモシステム開発までを短期間・低コストで実現することで、中小・ベンチャー企業などのAIチップ開発加速を目指します。

図1 AIチップ設計拠点の機能

目覚ましく進展するIoT社会において、さまざまな形式を含む巨大なデータ(ビッグデータ)から人々の生活に新たな価値を創造するための鍵となる技術として人工知能(AI)技術が注目されています。

このAI技術の根幹をなす半導体集積回路は、微細化が進み素子の集積度が高くなるとともに、より高度な情報処理が可能になる一方で、単位面積当たりのエネルギー消費の増大が極めて大きな課題となっています。特に汎用(はんよう)の半導体集積回路ではエネルギー消費が大きくなりやすいため、省エネルギーで効率的にAIを動作させる専用の半導体集積回路・デバイス(AIチップ)の開発が必要不可欠であり、世界的にもAIチップの開発競争が激化しています。

日本では、多くの中小・ベンチャー企業などが台頭し、AIチップの開発に取り組んでいます。しかし、AIチップの開発には、EDAツールやハードウエア・エミュレーター(H/Wエミュレーター)、標準IPコア、高性能なサーバーマシン、大容量のストレージなどからなる高価かつ大規模な半導体設計環境が必要であり、中小・ベンチャー企業などに革新的な構想があったとしても、AIチップの設計や試作に対する障壁になっています。

このような背景のもと、NEDO(国立研究開発法人新エネルギー・産業技術総合開発機構)は「AIチップ開発加速のためのイノベーション推進事業」(以下、本事業)において、国立研究開発法人産業技術総合研究所(産総研)、国立大学法人東京大学と共同で、東京大学本郷地区浅野キャンパス(東京都文京区)内の武田先端知ビルに「AIチップ設計拠点(通称:AIチップデザインセンター[以下、AIDC])」を整備しています。AIDCは2019年10月に試験運用を開始し、AIチップ設計に必要なEDAツールやH/Wエミュレーター、標準IPコアなどからなるAIチップの設計環境を整えるとともに、これらを活用するための設計フローなど、AIチップ設計のための共通基盤技術の開発、知見・ノウハウの蓄積や人材育成などを進めてきました。AIDCの試験運用に協力した中小・ベンチャー企業などの拠点利用者は、2023年1月時点までの合計で195名、74プロジェクトに達し、本事業で開発する共通基盤技術の実証や本拠点の有効性の確認を行ってきました。

そしてこのたび、2023年4月1日にAIDCの本格運用を開始します。AIDCは産総研の共用施設として位置付けられ、産総研と東京大学が共同で本格的な運用を行います。4月からAIDCは、本事業で構築した設計環境と、その利用方法・ノウハウなどを含めて提供し、中小・ベンチャー企業などのAIチップ開発加速を目指します。また、新規の技術開発も進め、AIチップ設計の多様なワンストップサービスの提供を目指します。

なお、2023年3月22日13時から、東京大学 武田先端知ビル 武田ホールにて、本事業の最終成果報告会を開催します。詳細は以下のリンク先をご覧ください。

AIDC最終成果報告会のお知らせ(https://ai-chip-design-center.org/aidc_debriefing2023/)

AIDCでは、EDAツールやH/Wエミュレーター、標準IPコア、高性能なサーバーマシン、大容量のストレージを整備しています。EDAツールとしては、上流設計に関係するEDAツール群はもちろんのこと、物理設計に関係するツール群が利用可能です。H/Wエミュレーターは、国内最大規模の23億ゲートの大規模回路で100億サイクルを数時間で検証可能です。標準IPコアについては、28 ナノメートル(nm)、12 nmプロセスで利用できる標準インタフェース回路などを準備しているほか、それら標準IPコアを搭載した評価チップと評価ボードを用いて、利用者が開発した回路と標準IPコアの接続などをH/Wエミュレーターにより事前に評価できます。

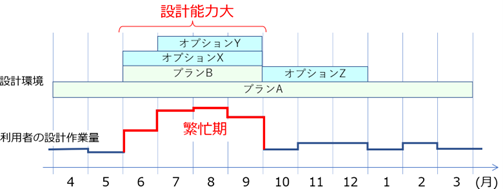

これらのツールは2023年4月1日以降、産総研の約款により定めたプランとオプションを組み合わせることで利用者の設計計画に合わせてフレキシブルに半導体設計環境を構築して使用することが可能です(図2)。

図2 設計作業量に合わせたフレキシブルな設計環境構築のイメージ

AIチップ向けIPの設計・評価プラットフォームは、中小・ベンチャー企業などが開発するアルゴリズムを実行するエンジンであるAIアクセラレーター向け設計・評価プラットフォームです。AIアクセラレーターを実環境で評価するには、AIアクセラレーターと標準システム回路を有するシステム・オン・チップ(SoC)、いわゆるAIチップを開発し、それを用いてシステムレベルでの評価が必要なため、多くのコストと時間がかかっています。そこでAIDCでは、共通基盤技術として標準システム回路や検証回路、テスト回路、評価ボード、ソフトウエア開発環境などを開発し、中小・ベンチャー企業などにこれら共通技術をAIアクセラレーター向け設計・評価プラットフォームとして提供します。AIDC利用者は本プラットフォームを利用することで、短期間(従来比45 %以下)かつ低コストで、各企業独自のAIアクセラレーター搭載チップの設計、試作から組み立て、評価、デモシステム構築まで一括して行う環境を入手することができます。

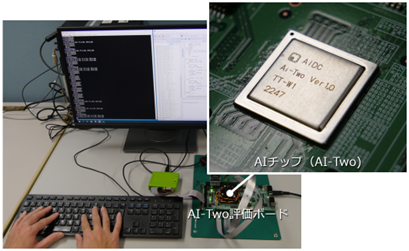

すでに28 nmプロセスによる設計・評価プラットフォーム「AI-One」の動作を確認しており、参加6機関(うち、企業5社)によるAIアクセラレーターのデモンストレーションに成功しています。さらに12 nmプロセス(FinFET)による設計・評価プラットフォームの実証も進めており、現在、中小・ベンチャー企業2社の協力を得て3種類の独自AIアクセラレーターを搭載した実証チップ「AI-Two」を設計し、外部の製造会社で試作した実チップの組み立てと評価ボードへの実装を完了、チップ評価を開始しました。現在、各協力会社で自身のAIアクセラレーターの評価をしており、これまでに3種類のAIアクセラレーター全てが設計通りの周波数で動作することを確認しました(図3)。今後、AIアクセラレーターの機能を確認し、2023年3月までに設計・評価プラットフォームとして整備を完了します。

図3 現在実証中の設計・評価プラットフォーム「AI-Two」

AIDCを利用するには、AIDCのWEBサイト(https://ai-chip-design-center.org)から利用申請が必要です。WEBサイトには、AIDCが主催するフォーラムや各種セミナーのお知らせ、ニュースなども掲載しています。

産総研 広報部 報道室

TEL:029-862-6216

E-mail:hodo-ml*aist.go.jp(*を@に変更して使用してください。)