独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】ナノスケール計測・プロセス技術研究グループ 福田 浩一 主任研究員らは、大規模集積回路(LSI)の基板上に転写する回路パターン(リソグラフィーパターン)の詳細な形状を反映できる回路特性解析システムを開発した。

今回開発したシステムは、リソグラフィーシミュレーションによって予測した微細パターンの詳細な形状をTechnology CAD(TCAD)に反映させて回路特性を解析する。このシステムを用いてフィンFETで構成したSRAMの回路特性を予測し、フィンFET特有のパターン形状の影響を明らかにした。また、このシステムは製造プロセスからデバイス構造の回路特性までを一貫してシミュレーションすることで、LSIの製造工程を最適化できるため、次世代大規模集積回路の設計への貢献が期待される。なお、この技術の詳細は、2013年4月16~18日に神奈川県横浜市で開催されるPhotomask Japan 2013 (PMJ 2013)で発表される。

|

|

リソグラフィーパターンからSRAMの安定性を解析 |

近年、LSIの発展に伴い、そこで使われるトランジスタは微細化の限界に迫ろうとしており、最新のフォトリソグラフィー技術を用いてLSIパターンを描画しても、パターンが理想形状からずれてしまう問題が顕著になってきている。そのようなずれが回路性能にどのような影響を及ぼすかを把握でき、製造性を考慮した設計を行える手法を構築することが急務とされている。

最近、このような設計手法を実現するために、製造の際の描画形状ばらつきをデータベース化して活用する技術や、フォトマスクパターンを補正する技術が実用化されてきているが、製造工程で実際にできる微細なパターン形状を予測し、その形状を反映させて回路特性を検討できる技術は整備されていない。

産総研は、この問題を解決するために、最新のフォトリソグラフィーシミュレーション技術と、TCAD技術を連携させることにより、リソグラフィーパターンの微細形状を反映した回路特性の解析システムの構築に取り組んだ。

なお、この研究の一部には、エーエスエムエル・ジャパン株式会社との共同研究の成果であるシミュレーション結果と、同社のフォトリソグラフィーシミュレーターTachyonを使用した。また、株式会社半導体理工学研究センターとの共同研究により提供されているTCADシステムHyENEXSSを使用した。

今回開発した回路特性解析システムは、フォトリソグラフィーシミュレーターなどで予測したLSIの微細パターンがあれば、トランジスタのデバイス構造から回路特性までをTCAD技術である半導体製造プロセスシミュレーションや半導体デバイスシミュレーションにより微細パターンを反映させて予測できる。予測された微細パターンの形状は標準的なGDS-IIなどのレイアウトフォーマットで用意する。まず、予測された微細パターンの形状から、半導体製造プロセスシミュレーションにより半導体の製造工程を再現して、トランジスタなどLSIで用いられる複数の素子の微細なデバイス構造を予測する。さらに、そのデバイス構造から、半導体デバイスシミュレーションにより個々の素子の電気的特性を予測し、素子同士をつなげた回路についても、デバイス・回路混合シミュレーションによって回路特性が予測できる。

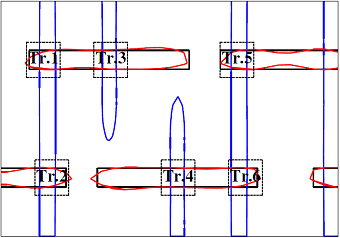

図1にフィンFETを用いたSRAM回路のフォトマスクパターンと、リソグラフィーシミュレーターによって予測した作製されるパターンを重ねて示す。このような微細なLSIでは、四角いフォトマスクを用いても、リソグラフィー工程の露光の際の光強度の分布により作製されるパターンでは、ずれがみられる。

|

図1 フィン型FETを用いた6トランジスタSRAMの設計上の長方形フォトマスクパターンと、リソグラフィーシミュレーションによる予測パターンを重ねたもの

黒い破線がひとつひとつのトランジスタを形成している場所。黒の実線が設計上のゲートパターン、赤がシミュレーションで予測されたゲートパターン、青はシミュレーションで予測されたフィンのパターンである。 |

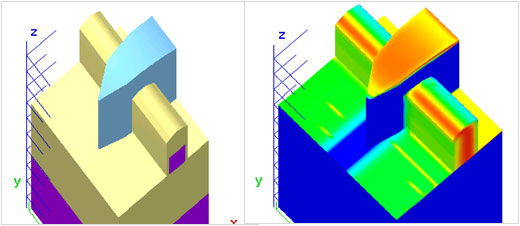

図2に計算された個々のトランジスタのパターンを元に、フィンFETの製造工程で形成されるトランジスタの素子形状および不純物分布を、半導体製造プロセスシミュレーションで予測した結果を示す。左は材質・形状、右はイオン注入で導入されたドーパント不純物分布の例である。このように実際に製造されるトランジスタは微細パターン形状の影響を受け、設計された長方形パターンの形状とは異なる形に形成され、また、トランジスタの特性を左右するドーパント不純物分布にも影響を与える。

|

図2 半導体製造プロセスシミュレーションにより計算された図1のTr.1部分のフィンFETの材質・形状(左)とドーパント不純物分布(右)の例

リソグラフィーシミュレーションで予測されたパターン形状を反映している。 |

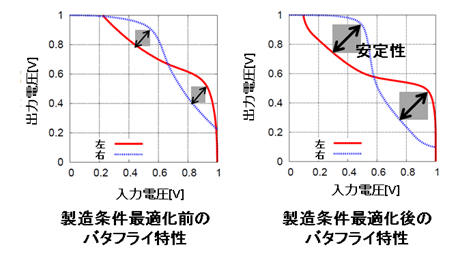

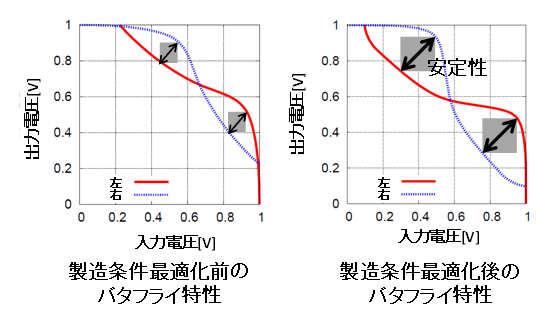

図3にデバイス・回路混合シミュレーションにより計算した、SRAMの

バタフライ特性と

静的雑音余裕(SNM)特性の予測例を示す。左は製造条件を最適化する前の特性であり、SNMが小さいため歩留まりが悪くなると考えられる。右は製造条件を最適化した後の特性であり、SNMが大きくなり改善されている。このように今回開発したシステムを用いることで、リソグラフィーパターンから得られるデバイス構造を反映して、回路特性を一貫してシミュレーションすることができる。これによりマスクパターンから得られる回路特性に対し、LSIの製造工程を最適化することで、微細なパターンのLSIを従来よりも高い歩留まりで生産することが可能となる。

|

図3 今回開発したシステムによって予測されたフィンFETのSRAM回路の静的雑音余裕(SNM)

電圧-電圧特性に描かれた矢印がSNM値であり、回路安定性の指標となる。左の製造プロセス最適化前に比べ、右の最適化後では大幅にSNMが改善されている。 |

今回開発した回路解析システムを大規模集積回路の開発者に提供することにより、微細デバイスを用いたLSI回路の実現を加速させる。また、つくばイノベーションアリーナ ナノテクノロジー拠点(TIA-nano)および産総研 スーパークリーンルーム(SCR)産学官連携研究棟で、産業界と大学が一体となって次世代技術の研究を進めるための共用インフラとして活用する。