独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【研究部門長 和田 敏美】先端シリコンデバイスグループ【研究グループ長 鈴木 英一】大内 真一 研究員、昌原 明植 主任研究員らは、システムLSIの面積の50%以上を占めるSRAMの動作安定性を、従来技術の1.5倍に高める、高性能な新回路を考案した。

今回考案されたSRAM回路は、素子間特性ばらつきの小さな、フィン型マルチゲート電界効果型トランジスタ(フィン型FET)と呼ばれる立体型新構造トランジスタと、これに電流駆動力を調整する機能を加えた4端子フィン型FETによって構成される。4端子フィン型FETを書き込み・読み出し回路と記憶保持部を接続する部位に用い、この部位の電流駆動力を書き込み・読み出しの動作に応じて動的に切り替えることによって、それぞれの動作安定性を向上させることができる。シミュレーションによる検討の結果、従来の平面型トランジスタでSRAM回路を実現する場合に比べて、1.5倍の動作安定性が書き込み・読み出しの両動作で実現されるとの見通しを得た。22nm世代トランジスタ技術において、従来と同じ構成のSRAMを用いると歩留まりの問題が生じるが、本SRAM回路を用いれば解決できることになる。

この成果は、9月17-19日に米国サンノゼ(シリコンバレー)で開催される国際会議「カスタム集積回路会議」(2007 Custom Integrated Circuits Conference)の注目論文として発表される。

|

|

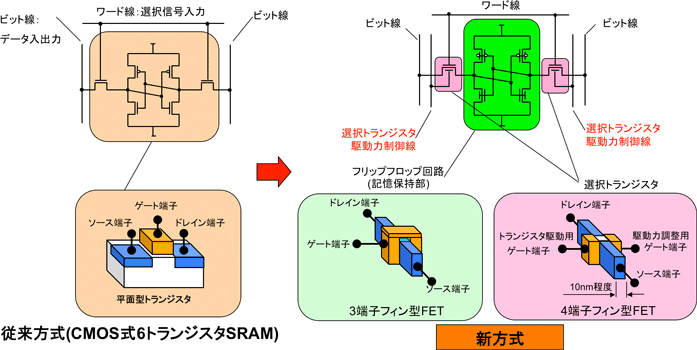

図1 従来方式に対する新方式SRAMの回路構成と素子の模式図 |

集積回路は、その最小構成単位である素子の寸法を縮小し、素子集積度を高めることによって、性能を向上させることができる。この集積回路技術の進展は、IT社会の発展をハードウェア面から支える原動力となってきた。素子微細化は、集積回路製品のコスト削減にもつながるため、微細素子開発の熾烈な競争が続いている。技術開発の難度は年々高くなってきており、2013年以降に市場投入が想定されている22nm世代トランジスタ技術では、素子寸法が現在の半分に縮小されるのに伴い、素子性能のばらつきが重大な問題になると危惧されている。特に、システムLSIやマイクロプロセッサの50%以上の面積を占めるSRAMでは、チップ上で最小寸法のトランジスタを多用するために、この問題の影響を受けやすい。回路的な工夫を想定しない単純な見積もりによれば、22nm世代で従来と同じ構成のSRAMを用いると、携帯機器などに搭載される量産型システムLSIやマイクロプロセッサのSRAMでは、歩留まりがゼロになりかねないと懸念される。よって、素子技術面では素子寸法縮小とこれに伴う素子性能ばらつきに強い新構造素子が、回路技術面では素子性能ばらつきや雑音に対する動作安定性が高められるSRAMの新回路方式が、強く求められていた。

産総研の前身である工業技術院電子技術総合研究所(以下「電総研」という)は、素子寸法が縮小されても性能劣化を起こさず理想的に性能向上が可能な2重ゲート電界効果型トランジスタ(XMOSFET)を、1984年に世界に先駆けて提案した。これは、ゲートを3次元立体構造にしたフィン型FETと呼ばれる立体型新構造トランジスタへと発展し、トランジスタの微細化限界を打破できる究極の極微細構造トランジスタとして世界中で注目されている。

産総研は、このフィン型FETを4端子素子とし、素子の電流駆動力を電気的に調整することを可能にした4端子フィン型FETを提案し、2003年に微細デバイスでは世界初の動作検証に成功した。4端子フィン型FETは、3端子型のフィンFETと同一集積回路基板上に集積することが可能であり、その実証も既に終えている。

産総研では、このようなフィン型FETの有効性が最大限に発揮される集積回路製品に関して研究を続けてきた。今回考案したSRAM回路は、3端子型と4端子型両方のフィン型FETを効果的に用い、SRAMの動作安定性を大幅に拡大するものである。今回は、試作による原理実証に先立ち、シミュレーションによりその効果を確認した。

新SRAM回路の1ビット分の構成要素(セル)、ならびにこれに用いられる素子模式図を、従来型と比較して図1に示す。従来主流のCMOS式6トランジスタSRAMでは、平面型トランジスタを6つ用いてセルを構成していた。これに対して新方式では、4つのトランジスタで構成される記憶保持部(フリップフロップ回路)を3端子フィン型FETで構成し、記憶保持部とビット線を接続してデータ入出力を行う2つの選択トランジスタを、4端子フィン型FETにより構成する。

|

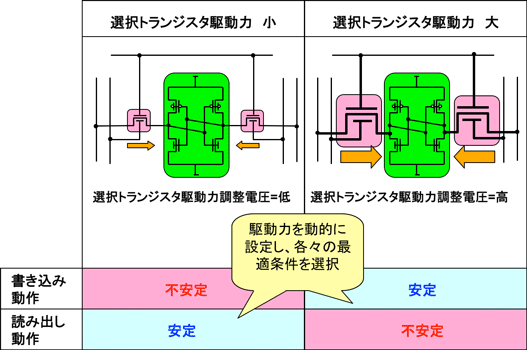

図2 新方式SRAM回路の動作原理説明図

|

一般に、SRAMセルでは、記憶保持の動作中は選択トランジスタがオフの状態にあり、記憶は安定して保持される。一方、書き込みや読み出しを行う場合には、選択トランジスタは選択信号に従ってオン状態になる。ここで、安定した書き込みを行うためには、フリップフロップ回路がビット線と強く結合されるのが望ましいが、逆にこの結合が強すぎると読み出し時の記憶破壊につながる。このように、従来、書き込み動作と読み出し動作安定性の間には設計の矛盾(トレードオフ)が存在していた(図2参照)。素子間の特性ばらつきが大きくなると、このトレードオフのために、書き込み動作と読み出し動作の安定性を両立するSRAMの設計が成り立たなくなる。

新方式では、選択トランジスタを電流駆動力可変の4端子フィン型FETにしたことにより、書き込み時には電流駆動力を大きくしてビット線-フリップフロップ回路間の結合を高め、逆に読出し時には電流駆動力を小さくし結合力を低めることが可能になり、トレードオフを解消できる。結果として、書き込み時・読み出し時双方で安定性を最大化できる。これは、回路の雑音に対する強靭性が向上すると同時に、雑音と等価な効果を持つ素子特性のばらつきに対する強靭性が増すことを意味する。

|

|

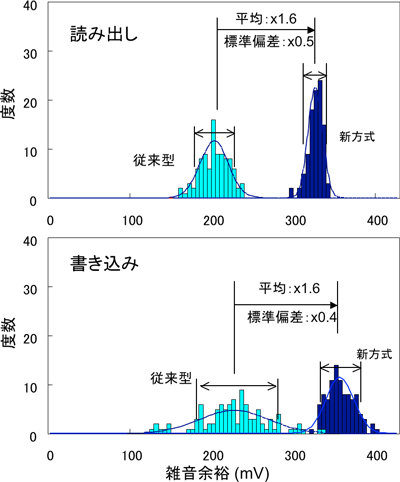

図3 22nm世代トランジスタ技術における従来型SRAMと新方式SRAM回路の雑音余裕に関する比較(市販のシミュレーションソフトを使用)。ばらつきは乱数を使って発生させ、100回の試行を行った。雑音余裕が高まり、分布も小さく抑えられ、歩留まりの改善につながる。 |

動作安定性を表す指標としては、静的雑音余裕がしばしば用いられる。図3は、この雑音余裕を書き込み動作と読み出し動作それぞれについて、シミュレーションしたものである。シミュレーションにおいては、22nm世代トランジスタ技術を仮定した。計算の結果、22nm世代相当の従来型平面トランジスタで構成されるSRAM回路に比べて、今回考案したSRAM回路は平均で1.5倍以上の動作安定性を実現するとの見通しを得た。更に、素子特性ばらつきに起因する動作安定性の分布も小さく抑えられることが分かった。これは、大規模回路では統計的に発生することが避けられない、設計目標から特性が大きく外れたSRAMセルにおいても、十分な動作安定性が保たれることを意味し、歩留まりを改善することにつながる。今回得られた計算結果の単純な換算を行うと、2013年に市場投入想定の量産型システムLSIに搭載されるSRAMでも十分な歩留まりが得られることになる。

今後、今年度から実施の、経済産業省の研究開発プロジェクト「ナノエレクトロニクス半導体新材料・新構造技術開発-うち新材料・新構造ナノ電子デバイス」を通じて、原理実証を行う。