国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)スピントロニクス研究センター【研究センター長 湯浅 新治】 半導体スピントロニクスチーム付 齋藤 秀和 企画主幹は、独自に開発した単結晶酸化ガリウム(Ga2O3)の成膜プロセスを用いて、半導体Ga2O3をトンネル障壁層とした単結晶だけからなるトンネル磁気抵抗(TMR)素子を開発した。

今回開発したTMR素子の磁気抵抗変化率(MR比)は室温で92 %と極めて大きい。このTMR素子は、メモリー機能をもつ縦型のスピン電界効果型トランジスタ(縦型スピンFET)の基本構造となるもので、待機電力ゼロのノーマリー・オフ・コンピューターへの貢献が期待される。この技術の詳細は、2016年9月20日(現地時間)に米国の学術誌Physical Review Appliedのオンライン版に掲載される。

なお、この研究開発は、内閣府 革新的研究開発推進プログラム(ImPACT)「無充電で長期間使用できる究極のエコIT機器の実現(平成26~30年度)」による支援を受けて行った。

|

|

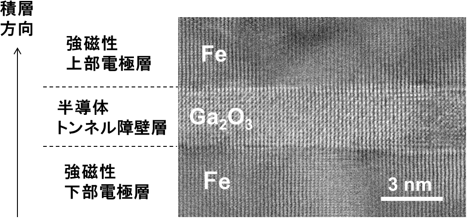

今回開発したTMR素子断面の電子顕微鏡写真

下部の鉄(Fe)電極層から、半導体Ga2O3障壁層、上部のFe層まで、各層の原子が積層方向に直線的に並んでおり、全単結晶TMR素子であることがわかる。

|

コンピューターなどのIT機器の抜本的な省電力化には、待機電力の削減が必要不可欠である。しかし、現在のコンピューターの主要メモリーや論理回路に利用されるトランジスタは、電源を切ると情報が失われてしまう「揮発性」素子であるため待機電力の大幅な削減は難しい。そのため、待機電力を大幅に低減できる、電源を切っても情報が失われない「不揮発性」のFETが求められている。

スピンFETは、電子スピンを利用することにより不揮発性のメモリー機能を得ることができるため、世界的に研究が行われている。しかし、メモリー機能の性能指数であるMR比は、実用的には、数十~100 %以上が必要とされているが、これまでのスピンFET研究においては、現行のFETと同じ横型素子が用いられており、MR比は室温では0.1 %程度であった。

産総研は、これまで新規TMR素子の開発とそれを利用した磁気メモリーの開発に取り組んできており、世界トップクラスのトンネル素子作製技術をもっている。また、スピンFETの構築に必要な強磁性金属/半導体間接合に関しても長年取り組んでおり、同様に世界トップレベルの技術をもっている。

最近、MR比を大幅に向上させるために、全単結晶TMR素子をベースとした縦型スピンFETが提案されている。強磁性半導体を電極とし、非磁性半導体を障壁層とした全単結晶TMR素子には、極低温では100 %以上の高いMR比を示すものもある。しかし、この素子には室温でMR比がほぼゼロになってしまうという大きな問題がある。産総研では、これまで培ってきたTMR素子作製技術や異種材料間膜成長技術により、強磁性金属電極と半導体障壁層を組み合わせて、高いMR比を示す全単結晶TMR素子を作製できると考え、その開発に取り組んだ。

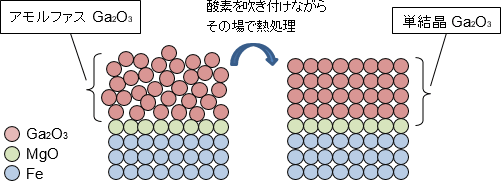

今回、半導体トンネル障壁層材料として酸化物半導体であるGa2O3を用いた。この半導体は、結晶構造が複雑であるため、鉄(Fe)などの一般的な強磁性電極と組み合わせた単結晶TMR素子の作製は困難と考えられていた。そのため、これまでTMR素子のトンネル障壁層としてはほとんど注目されていなかった。産総研は独自の成膜プロセスを開発して、Fe強磁性電極とGa2O3トンネル障壁層から成る全単結晶TMR素子を作製した。図1に開発した成膜プロセスを示す。成膜には蒸着の一種である分子線エピタキシー法を用いた。まず、下部電極である単結晶Fe上に非常に薄い(厚さ0.4~0.7ナノメートル)単結晶酸化マグネシウム(MgO)層を成長させる。この上にアモルファスGa2O3膜(厚さ1.5~3.0ナノメートル)を室温付近で製膜し、その後、適量の酸素を膜に吹き付けながら500 ℃程度までの熱処理を行うと、極めて高品位の単結晶Ga2O3膜が得られる。この単結晶Ga2O3膜上には、単結晶Fe上部電極を直接成長させることができる。なお、得られた単結晶Ga2O3膜を詳細に分析したところ、スピネル型という単純な結晶系の構造であった。

|

|

図1 今回開発した単結晶Ga2O3膜作製方法 |

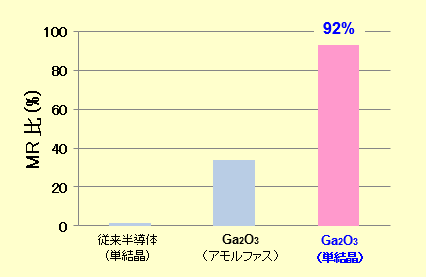

図2に今回開発したTMR素子の室温でのMR比を示す。比較のため、従来の半導体障壁層をもつ全単結晶TMR素子(電極は強磁性金属)での最高値と、今回、Ga2O3を単結晶化した効果を調べるため作製したアモルファスGa2O3障壁層(上部電極のFeは多結晶)のTMR素子の値も示す。Ga2O3層を単結晶化することによりMR比が大幅に増大し、半導体トンネル障壁層の素子としてはこれまでで最も高い値(92 %)を示した。MR比の増大は、単結晶MgOを用いたTMR素子と同様に、トンネル障壁層と上部強磁性電極の単結晶化により電子が波の性質を保ったまま伝搬できるようになったためと考えられる。

|

|

図2 半導体障壁層のTMR素子の室温でのMR比の比較 |

今後は、MR比の一層の向上を図ると共に、Ga2O3膜に電界をかけて出力電流を制御するためのゲート構造の設計と動作実証を行い、5年後を目途に実用的な性能の縦型スピンFETを開発する。これにより、超省電力のノーマリー・オフ・コンピューターの実現に繋げる。