独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノ電子デバイス研究センター【研究センター長 金山 敏彦】極限構造トランジスタ研究チーム 太田 裕之 研究チーム長、右田 真司 主任研究員は、0.5 nmの非常に薄い高誘電率ゲート絶縁膜を製造する新しい技術を開発した。

この技術は、現行の半導体デバイス製造プロセスを改良したものである。高誘電率材料の結晶化過程に注目し、結晶成長を精密にコントロールする熱処理プロセスを取り入れた結果、シリコン基板との界面に低誘電率層が生成しない高誘電率結晶膜の合成技術を開発した。この技術で合成した高誘電率結晶膜をMOSトランジスタのゲート絶縁膜として用いると、シリコン酸化膜(SiO2)換算膜厚で0.5 nmまで薄膜化することができ、漏れ電流量が6桁小さくなることを確認した。MOSトランジスタのゲート絶縁膜の漏れ電流は集積回路の消費電力の大きな部分を占めているが、今回開発した高誘電率ゲート絶縁膜は、より低消費電力な集積回路の製造に貢献することが期待される。

本研究開発は、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)の「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト」の委託を受けて行ったものであり、技術の詳細は、2010年12月6~8日にサンフランシスコで開催されている国際会議「International Electron Devices Meeting」で発表された。

|

|

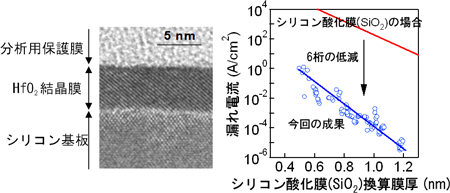

図1 シリコン基板上に直接成長した高誘電率結晶膜(HfO2)の電子顕微鏡写真(左)と漏れ電流の低減(右)

|

近年、携帯電話、パソコン、高機能テレビなどの普及によって、社会全体での電子機器の消費電力量が増大傾向にあるが、これらの消費電力を低減することは、CO2排出量の削減にも貢献する重要な技術課題である。電子機器の中枢機能である集積回路は、数億個のMOSトランジスタを集積して構成されており、一つ一つのMOSトランジスタのゲート絶縁膜の漏れ電流を低減することが、電子機器全体の低消費電力化につながる。

トランジスタのゲート絶縁膜の漏れ電流を低減するために、世界中の半導体メーカー、大学、研究機関などで高誘電率材料を用いたゲート絶縁膜の研究開発が行われてきた。現在、シリコン酸化膜換算膜厚で1 nmという薄さのゲート絶縁膜が開発され、この技術を用いた集積回路が製品化されている。半導体業界では、2013年以降には0.65 nm、2015年には0.53 nmの薄さを必要としており、世界中でこの目標の実現に向けた研究開発が行われている。

産総研は、高誘電率ゲート絶縁膜の研究開発を行ってきており、原子層成長技術と急速熱処理技術を組み合わせた不純物低減技術の開発、高誘電率材料とシリコン酸化膜の界面に発生するダイポールがトランジスタ動作のしきい値電圧や移動度低下に及ぼす影響の解明など、そのポテンシャルは世界トップクラスにある。

本研究開発は、NEDOの「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト」の委託を受けて行ったものである。本プロジェクトは、産総研、大学、デバイスメーカーや装置メーカーなどから成る産学官連携プロジェクトとして、次世代の半導体材料ならびにプロセス基盤技術の開発を行っている。産総研は、その中でバリスティックCMOS基盤技術の開発を全面的に担当している。

今回の技術は、高誘電体材料の結晶膜の合成方法を新たに考案し、開発に至ったものである。これまでにも結晶膜で高誘電率ゲート絶縁膜を作る試みは世界中の企業や研究機関で行われてきた。実際に、研究用途の特殊な成膜方法を用いて、結晶膜の優秀性を示す成果も得られている。しかし、生産用途の製造プロセス装置で高誘電体材料の結晶膜を合成すると、低誘電率層の生成による膜厚増加や漏れ電流の増大が発生するため、実用レベルの性能をもつ絶縁膜の作製は非常に困難とされてきた。そこで今回は、生産用途の装置を用いながら、結晶化の過程を改良することで、従来解決されていなかった問題の克服に取り組んだ。

図1の左は、今回実現した、シリコン基板上に合成した高誘電体材料であるハフニウム酸化物(HfO2)結晶膜の高分解能電子顕微鏡写真である。基板のシリコン結晶の原子配列に対して、ハフニウム酸化物の結晶の原子配列が整合して成長している様子が現れている。

図1の右は、シリコン基板上に合成したHfO2結晶膜にゲート電極を形成して測定したシリコン酸化膜換算膜厚と漏れ電流値の関係である。今回開発した技術により、シリコン酸化膜の場合と比較して6桁にもおよぶ漏れ電流の低減を実現した。最も薄い場合には0.5 nmの性能を1 A/cm2の漏れ電流で達成している。開発した技術が実用化されれば、今後10年にわたるゲート絶縁膜の開発に目処が立つと考えている。

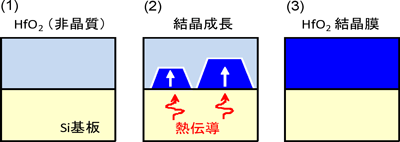

開発したプロセスのモデルを図2に示す。最初にシリコン基板上に原子層成長法で非晶質のHfO2膜を堆積する。続いて高温熱処理で非晶質膜を結晶化させる処理を行うが、このときに、シリコン基板からの熱伝導を利用して、基板界面からの結晶化が始まるようにする。これによって、界面に低誘電率層が生成することを抑止できる。さらに結晶成長の方向がそろっていることで、隙間のない、ち密な結晶膜が得られ、漏れ電流の増大も抑えることが可能になる。

今回開発した技術は、現行の半導体デバイスの製造現場と同様の材料ならびに同等の製造装置を用いて実現したものであり、実用化への困難が少ないと考えている。

|

|

図2 開発した高誘電率結晶膜(HfO2)の合成方法。(1) シリコン基板上に非晶質状態のHfO2膜を堆積、(2) 基板からの熱伝導を利用して界面からの結晶成長を促進、(3) 隙間の無い、ち密な結晶膜が完成。

|

今後は作製した構造のプロセス耐性、電気特性のばらつきや信頼性を、さらに系統的に試験することで、将来の低消費電力デバイスの開発に貢献したい。