## 仕 様 書

# 1. 件名

FPGA システム設計

#### 2. 作業の概要

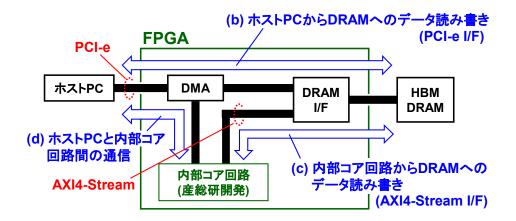

産業技術総合研究所(以下、産総研という。)先端半導体研究センターでは、 高効率 AI アクセラレータの研究を実施している。本研究では、ホスト PC に PCI-express を介して、HBM (High Bandwidth Memory) を搭載した FPGA が接 続されたシステムを想定している。産総研では、この FPGA 上で動作する AI ア クセラレータ回路を設計しており、その検証に必要となる本回路とホスト PC・ HBM を接続する為のインタフェース(回路、及び、ホスト PC 上で動作する制 御用ソフトウェア)を設計するものである。

### 3. 作業項目

(1) FPGA システム設計

#### 4. 作業項目別仕様内容

- (1) FPGA システム設計

- (a) 以下の(b)-(d)の3つの機能を有する FPGA システムを開発する。 概要を 別紙の図1に示す。開発の対象とする FPGA は、AMD 社製 VCU128 評価ボード(AMD UltraScale+ VU37P 搭載)とする。DRAM は HBM とする。また、ホスト PC の OS は、Windows 11 又は Linux と する。

- (b) ホスト PC から FPGA に接続された HBM へのデータの書き込み、及び、HBM からホスト PC へのデータの読み込みができる機能を有すること。なお、ホスト PC からは、PCI-Express 3.0 (Gen 3)インタフェースでデータの読み書きができること。また、これを実現する為の、ホスト PC 上のソフトウェアのソースコードを提供すること。

- (c) FPGA 内部コア回路から、FPGA に接続された HBM へのデータの書き込み、及び、HBM から FPGA へのデータの読み込みができる機能を有すること。なお、内部コア回路からは、AXI4-Stream インタフェースを介して、HBM とデータの読み書きができること(読み書

きする HBM のアドレスは、ホスト PC から設定可能であること)。 内部コア回路自体は産総研が開発する。

(d) ホスト PC から内部コア回路への動作開始信号の送信、また、内部コア回路からの動作終了信号の受信、などホスト PC と内部コア 回路間で双方向の通信が行える機能を有すること。

#### 5. 貸与品

AMD 社製 VCU128 評価ボード 一式

#### 6. 特記事項

(1) 設計要員の能力、要件

請負業者として、XDMA IPとHBM IPを使用したAMD UltraScale+ FPGAの設計実績(納入実績)があることを、技術審査時にエビデンスと共に示すこと。

#### 7. 納入の完了

本件は、「8. 納入物品」に記載された納入物品が過不足なく納品され、仕様書を満たしていることを確認して、納入の完了とする。

#### 8. 納入物品

回路の Vivado Project ファイル

… 一式

② ホスト PC 用のソフトウェア(ソースコードなど)

… 一式

- ③ FPGA で動作させる為の手順書(合成・コンパイル手順など) … 一式

- ※ ソースコード・手順書は電子媒体とすること

- ※原則として USB メモリ等の外部電磁的記録媒体以外で納入すること。

#### 9. 納入期限及び納入場所

納入期限: 2025 年 12 月 26 日

納入場所:国立研究開発法人産業技術総合研究所

先端半導体研究センター

つくばセンター中央事業所 2 群 2-13 棟 311 室

茨城県つくば市梅園 1-1-1

## 10. 付帯事項

● 本仕様書の技術的内容及び知り得た情報については、守秘義務を負うものとする。

- 本仕様書の技術的内容に関しては、請求担当者の指示に従うこと。また、 本仕様書に定めのない事項及び疑義が生じた場合は、会計担当者と協議 のうえ決定する。

- 納入物品の Vivado Project ファイルと、ホスト PC 用のソフトウェア (ソースコード) は、産総研が自由に改変できる権利を有すること。

図 1: 開発委託する FPGA システムの概要 (内部コア回路が産総研の開発する AI アクセラレータ回路に相当)