# 薄さ0.5ナノメートルのゲート絶縁膜

## 集積回路の低消費電力化に貢献

右田 真司 みぎた しんじ s-migita@aist.go.jp

ナノエレクトロニクス研究部門 シリコンナノデバイスグループ 主任研究員 (つくばセンター)

大学卒業後、電総研を経て産総研に入所。各種酸化物薄膜の合成とデバイス応用に従事してまいりました。現在はSOIトランジスタ製造技術を軸にして、高誘電率ゲート絶縁膜やメタルソース・ドレインといった新材料・新技術を融合した、新機能デバイスの開発を目指しています。

### 関連情報:

○ 共同研究者太田 裕之(産総研)

#### プレス発表

2010年12月8日「0.5 nmの非常に薄い高誘電率 ゲート絶縁膜を開発」

#### ゲート絶縁膜の重要性

携帯電話やパソコンなどあらゆる情報機器に は集積回路 (LSI) が多数搭載されており、その LSIの中では数億個のトランジスタが高速で演 算を行っています。ゲート絶縁膜はこのトラン ジスタを構成する材料で、電流をスイッチする 重要な役目を担っています。ゲート絶縁膜を薄 くすると、演算速度が速くなり、動作電圧も下 げられるので、LSIの高性能化や低消費電力化 につながります。しかし同時に漏れ電流の増大 という問題を引き起こし、LSIの大きなエネル ギー浪費を招きます。長年にわたってゲート絶 縁膜にはシリコン酸化膜 (SiO<sub>2</sub>) が使用されてき ましたが、その材料限界が明らかになり、近年 ゲート絶縁膜を高誘電率材料に置き換える研究 開発が世界中のデバイスメーカーで進められて います。

#### 開発したゲート絶縁膜

今回私たちは非晶質膜の結晶化反応に着目して、薄膜内部の伝熱現象を利用した熱処理技術を考案し、高誘電率材料の結晶膜をシリコン基板上に直接合成することに成功しました。

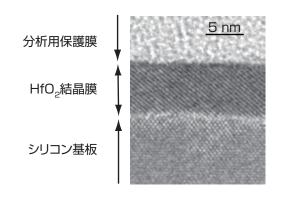

左図は、シリコン基板上に合成した高誘電率 材料(ハフニウム酸化物: HfO<sub>2</sub>)結晶膜の高分解 能電子顕微鏡写真です。結晶膜とシリコン基板 の結晶格子が直接結合して整列しており、エピ タキシャル薄膜が生成していることがわかりま す。

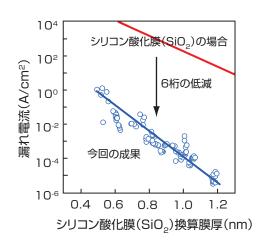

右図は、電気的に換算した絶縁膜厚(シリコン酸化膜換算膜厚)と漏れ電流の関係です。 $HfO_2$  結晶の誘電率は $SiO_2$ のおよそ5倍の大きさなので、2.5 nm厚さの $HfO_2$ 結晶膜によって0.5 nmという世界トップクラスの薄さの換算膜厚を実現できました。さらに、厚い $HfO_2$ 膜にトンネル電流を抑制する効果があるので $SiO_2$ 膜の場合に比べて漏れ電流を6桁も小さくすることができました。

この開発ではLSIの製造現場と同等の製造装置を使用しており、製造技術への展開は容易であると考えられます。また、この技術が実用化されれば、今後10年にわたるゲート絶縁膜の開発が大きく前進すると期待しています。

#### 今後の予定

今後はプロセス耐性、電気特性のばらつきや 信頼性などの系統的な評価へと展開し、低消費 電力デバイスの開発に貢献していきたいと考え ています。

シリコン基板上に直接成長した高誘電率結晶膜(HfO2)の電子顕微鏡写真(左)と漏れ電流の比較図(右)