# 二重絶縁ゲートMOSトランジスタを用いた回路

# XDXMOS:高速動作と待機時の低電力化を両立

# 特許 第4423392号 (出願2004.12)

#### 研究ユニット:

エレクトロニクス研究部門

# 適用分野:

MOS 集積回路

Patent Information のページでは、産総研所有の特許で技術移転可能な案件をもとに紹介しています。産総研の保有する特許等のなかにご興味のある技術がありましたら、知的財産部技術移転室までご遠慮なくご相談下さい。

## 知的財産部技術移転室

〒 305-8568 つくば市梅園 1-1-1 つくば中央第 2

TEL: 029-862-6158

FAX: 029-862-6159

E-mail: aist-tlo@m.aist.go.ip

## 目的と効果

この発明では、金属酸化膜半導体(MOS) 集積回路のあるまとまった回路単位で、高速動作と、定常時または待機時における消費電力の減少を両立させることを目的とし、二重絶縁ゲート電界トランジスタを用いてこれを実現する手法を提案しています。この手法を用いると、高速動作で静的消費電力の小さな相補型金属酸化膜半導体 CMOSトランジスタ回路、記憶メモリー素子(SRAM)セル回路、CMOS-SRAMセル回路、集積回路を実現できます。

### 技術の概要

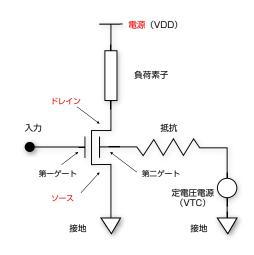

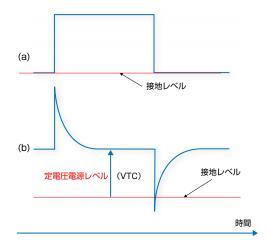

二重絶縁ゲート電界効果トランジスタとはチャネルを挟んで二つのゲート電極が対向して設けられている構造をしています。通常はこの二つの電極は接続して用いますが、この発明では図1の回路のように、第一ゲートには電気信号を入力し、第二ゲートは抵抗を通して一定の電位の電源に接続します。そうすると第一のゲートと第二のゲートの間の容量とこの抵抗で微分回路ができ、第二ゲートの電位は図2(b)

のように、図2(a)の第一ゲートの入力信号を微分したものとなります。その結果、過渡状態ではしきい値電圧が小さくなり、過渡電流を大きくして動作速度を速めることができ、定常状態では図1の一定電位の値をしきい値電圧が高くなるように設定して、漏れ電流を小さくできます。

### 発明者からのメッセージ

二重絶縁ゲート電界効果トランジスタは極微 細 MOSトランジスタとして理想的な特性を有するものとして産総研が提案してから久しいですが、最近になって将来これを採用することを表明する大手半導体製造メーカーもでてきました。巨大なLSI市場なので、そのインパクトは大きなものになります。ただ、製造のための新たなインフラ整備と従来素子と共通した課題も多く、産総研では微力ながらそれらの解決策を以前から探っています。この発明もその成果の一部で、国際学会(CICC2005)で発表しています。

図1 二重絶縁ゲート電界効果トランジスタを用いた回路構成

抵抗を通して第二ゲートを定電圧電源に接続する。

図2 (a) は第一ゲートへの入力波形、(b) は第二ゲート での波形で入力波形が微分されたもの。第二ゲートの 定常状態の電位レベルはVTCで、過渡状態のときのみ VTCより高くなるか低くなる。